EEPROM

| Computer memory types |

|---|

| Volatile |

| RAM |

| In development |

| Historical |

|

| Non-volatile |

| ROM |

| NVRAM |

| Early stage NVRAM |

| SAM |

| In development |

| Historical |

|

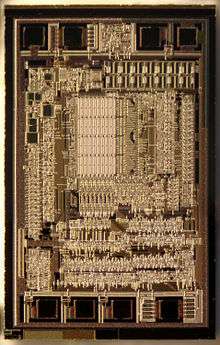

EEPROM (also written E2PROM and pronounced "e-e-prom", "double-e-prom" or "e-squared-prom") stands for electrically erasable programmable read-only memory and is a type of non-volatile memory used in computers and other electronic devices to store relatively small amounts of data but allowing individual bytes to be erased and reprogrammed.

EEPROMs are organized as arrays of floating-gate transistors. EEPROMs can be programmed and erased in-circuit, by applying special programming signals. Originally, EEPROMs were limited to single byte operations which made them slower, but modern EEPROMs allow multi-byte page operations. It also has a limited life for erasing and reprogramming, now reaching a million operations in modern EEPROMs. In an EEPROM that is frequently reprogrammed while the computer is in use, the life of the EEPROM is an important design consideration.

Unlike most other kinds of non-volatile memory, an EEPROM typically allows bytes to be read, erased, and re-written individually.

History

Eli Harari at Hughes Aircraft invented the EEPROM in 1977 utilising Fowler-Nordheim tunneling through a thin floating gate.[1][2] Hughes went on to produce the first EEPROM devices. In 1978, George Perlegos at Intel developed the Intel 2816, which was built on earlier EPROM technology, but used a thin gate oxide layer enabling the chip to erase its own bits without a UV source. Perlegos and others later left Intel to form Seeq Technology, which used on-device charge pumps to supply the high voltages necessary for programming EEPROMs.[3][4]

Electrical interface

EEPROM devices use a serial or parallel interface for data input/output.

Serial bus devices

The common serial interfaces are SPI, I²C, Microwire, UNI/O, and 1-Wire. These use from 1 to 4 device pins and allow devices to use packages with 8-pins or less.

A typical EEPROM serial protocol consists of three phases: OP-Code Phase, Address Phase and Data Phase. The OP-Code is usually the first 8-bits input to the serial input pin of the EEPROM device (or with most I²C devices, is implicit); followed by 8 to 24 bits of addressing depending on the depth of the device, then the read or write data.

Each EEPROM device typically has its own set of OP-Code instructions mapped to different functions. Common operations on SPI EEPROM devices are:

- Write Enable (WRENAL)

- Write Disable (WRDI)

- Read Status Register (RDSR)

- Write Status Register (WRSR)

- Read Data (READ)

- Write Data (WRITE)

Other operations supported by some EEPROM devices are:

- Program

- Sector Erase

- Chip Erase commands

Parallel bus devices

Parallel EEPROM devices typically have an 8-bit data bus and an address bus wide enough to cover the complete memory. Most devices have chip select and write protect pins. Some microcontrollers also have integrated parallel EEPROM.

Operation of a parallel EEPROM is simple and fast when compared to serial EEPROM, but these devices are larger due to the higher pin count (28 pins or more) and have been decreasing in popularity in favor of serial EEPROM or flash.

Other devices

EEPROM memory is used to enable features in other types of products that are not strictly memory products. Products such as real-time clocks, digital potentiometers, digital temperature sensors, among others, may have small amounts of EEPROM to store calibration information or other data that needs to be available in the event of power loss. It was also used on video game cartridges to save game progress and configurations, before the usage of external and internal flash memories.

Failure modes

There are two limitations of stored information; endurance, and data retention.

During rewrites, the gate oxide in the floating-gate transistors gradually accumulates trapped electrons. The electric field of the trapped electrons adds to the electrons in the floating gate, lowering the window between threshold voltages for zeros vs ones. After sufficient number of rewrite cycles, the difference becomes too small to be recognizable, the cell is stuck in programmed state, and endurance failure occurs. The manufacturers usually specify the maximum number of rewrites being 1 million or more.[5]

During storage, the electrons injected into the floating gate may drift through the insulator, especially at increased temperature, and cause charge loss, reverting the cell into erased state. The manufacturers usually guarantee data retention of 10 years or more.[6]

Related types

Flash memory is a later form of EEPROM. In the industry, there is a convention to reserve the term EEPROM to byte-wise erasable memories compared to block-wise erasable flash memories. EEPROM occupies more die area than flash memory for the same capacity, because each cell usually needs a read, a write, and an erase transistor, while flash memory erase circuits are shared by large blocks of cells (often 512×8).

Newer non-volatile memory technologies such as FeRAM and MRAM are slowly replacing EEPROMs in some applications, but are expected to remain a small fraction of the EEPROM market for the foreseeable future.

Comparison with EPROM and EEPROM/flash

The difference between EPROM and EEPROM lies in the way that the memory programs and erases. EEPROM can be programmed and erased electrically using field electron emission (more commonly known in the industry as "Fowler–Nordheim tunneling").

EPROMs can't be erased electrically and are programmed via hot carrier injection onto the floating gate. Erase is via an ultraviolet light source, although in practice many EPROMs are encapsulated in plastic that is opaque to UV light, making them "one-time programmable".

Most NOR flash memory is a hybrid style—programming is through hot carrier injection and erase is through Fowler–Nordheim tunneling.

| Type | Inject electrons onto gate (mostly interpreted as Bit=0) |

Duration | Remove electrons from gate (mostly interpreted as Bit=1) |

Duration/Mode |

|---|---|---|---|---|

| EEPROM | field electron emission | 0,1...5 ms, bytewise | field electron emission | 0,1...5 ms, blockwise |

| NOR Flash memory | hot carrier injection | 0,01...1 ms | field electron emission | 0,01...1 ms, blockwise |

| EPROM | hot carrier injection | 3...50 ms, bytewise | UV light | 5...30 minutes, whole chip |

EEPROM manufacturers

- Atmel

- Hitachi

- Infineon

- Intersil

- Linear Technology

- Macronix

- Maxwell Technologies

- Microchip Technology

- Mitsubishi

- NXP Semiconductors

- National Semiconductor (no longer makes standalone EEproms)

- ON Semiconductor

- Renesas Technology

- ROHM

- Samsung Electronics

- STMicroelectronics

- Seiko Instruments

- Winbond

- Giantec

In popular culture

The Stanford Graduate Students in Electrical Engineering (GSEE) has annually hosted a dance (i.e. prom) called EEPROM[7] since 2012.

See also

- DataFlash

- Intel HEX - File format

- SREC - File format

- Programmer (hardware)

References

- ↑ "Electrically erasable non-volatile semiconductor memory" (PDF).

- ↑ http://archive.computerhistory.org/resources/access/text/2012/03/102745933-05-01-acc.pdf

- ↑ Rostky, George (July 2, 2002). "Remembering the PROM knights of Intel". EE Times. Retrieved 2007-02-08.

- ↑ "Seeq Technology » AntiqueTech".

- ↑ "Frequently Asked Questions -ROHM Semiconductor".

- ↑ System Integration - From Transistor Design to Large Scale Integrated Circuits

- ↑ "Stanford Graduate Students in Electrical Engineering (GSEE) - Facebook".