Intel 80486

The exposed die of an Intel 80486DX2 microprocessor | |

| Produced | From 1989 to 2007 |

|---|---|

| Common manufacturer(s) |

|

| Max. CPU clock rate | 16 MHz to 150 MHz |

| FSB speeds | 16 MHz to 50 MHz |

| Min. feature size | 1 µm to 0.6 µm |

| Instruction set | x86 including x87 (except for "SX" models) |

| Data width | 32 [1] |

| Address width | 32 [1] |

| Virtual address width | 32 Linear; 46 Logical [1] |

| Predecessor | Intel 80386 |

| Successor | Pentium (P5) |

| Co-processor | Intel 80487SX |

| Package(s) | |

The Intel 80486, also known as the i486 or 486 ("four-eighty-six"), is a higher performance follow-up to the Intel 80386 microprocessor. The 80486 was introduced in 1989 and was the first tightly[lower-alpha 1] pipelined x86 design as well as the first x86 chip to use more than a million transistors, due to a large on-chip cache and an integrated floating-point unit. It represents a fourth generation of binary compatible CPUs since the original 8086 of 1978.

A 50 MHz 80486 executes around 40 million instructions per second on average and is able to reach 50 MIPS peak performance.

The i486 does not have the usual 80-prefix because of a court ruling that prohibits trademarking numbers (such as 80486). Later, with the introduction of the Pentium brand, Intel began branding its chips with words rather than numbers.

Background

The 80486 was announced at Spring Comdex in April 1989. At the announcement, Intel stated that samples would be available in the third quarter of 1989 and production quantities would ship in the fourth quarter of 1989.[2] The first 80486-based PCs were announced in late 1989, but some advised that people wait until 1990 to purchase a 80486 PC because there were early reports of bugs and software incompatibilities.[3]

Improvements

| Intel 80486 registers | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

The instruction set of the i486 is very similar to its predecessor, the Intel 80386, with the addition of only a few extra instructions, such as CMPXCHG which implements a compare-and-swap atomic operation and XADD, a fetch-and-add atomic operation returning the original value (unlike a standard ADD which returns flags only).

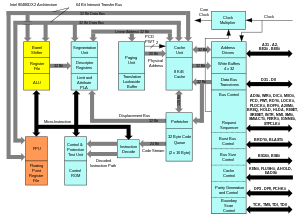

From a performance point of view, the architecture of the i486 is a vast improvement over the 80386. It has an on-chip unified instruction and data cache, an on-chip floating-point unit (FPU) and an enhanced bus interface unit. Due to the tight pipelining, sequences of simple instructions (such as ALU reg,reg and ALU reg,im) could sustain a single clock cycle throughput (one instruction completed every clock). These improvements yielded a rough doubling in integer ALU performance over the 386 at the same clock rate. A 16-MHz 80486 therefore had a performance similar to a 33-MHz 386, and the older design had to reach 50 MHz to be comparable with a 25-MHz 80486 part.[lower-alpha 2]

Differences between i386 and i486

- An 8 kB on-chip (level 1) SRAM cache stores the most recently used instructions and data (16 kB and/or write-back on some later models). The 386 had no such internal cache but supported a slower off-chip cache (which was not a level 2 cache because there was no internal level 1 cache on the 80386).

- Tightly coupled pipelining completes a simple instruction like ALU reg,reg or ALU reg,im every clock cycle (after a latency of several cycles). The 386 needed two clock cycles to do this.

- Integrated FPU (disabled or absent in SX models) with a dedicated local bus; together with faster algorithms on more extensive hardware than in the i387, this performs floating point calculations faster compared to the i386+i387 combination.

- Improved MMU performance.

- New instructions: XADD, BSWAP, CMPXCHG, INVD, WBINVD, INVLPG.

Just as in the 80386, a simple flat 4 GB memory model could be implemented by setting all "segment selector" registers to a neutral value in protected mode, or setting (the same) "segment registers" to zero in real mode, and using only the 32-bit "offset registers" (x86-terminology for general CPU registers used as address registers) as a linear 32-bit virtual address bypassing the segmentation logic. Virtual addresses were then normally mapped onto physical addresses by the paging system except when it was disabled. (Real mode had no virtual addresses.) Just as with the 80386, circumventing memory segmentation could substantially improve performance in some operating systems and applications.

On a typical PC motherboard, either four matched 30-pin (8-bit) SIMMs or one 72-pin (32-bit) SIMM per bank were required to fit the 80486's 32-bit data bus. The address bus used 30-bits (A31..A2) complemented by four byte-select pins (instead of A0,A1) to allow for any 8/16/32-bit selection. This meant that the limit of directly addressable physical memory was 4 gigabytes as well (230 32-bit words = 232 8-bit words).

Models

There are several suffixes and variants. (see Table). Other variants include:

- Intel RapidCAD: a specially packaged Intel 486DX and a dummy floating point unit (FPU) designed as pin-compatible replacements for an Intel 80386 processor and 80387 FPU.

- i486SL-NM: i486SL based on i486SX

- i487SX (P23N): i486DX with one extra pin sold as an FPU upgrade to i486SX systems; When the i487SX was installed it ensured an i486SX was present on the motherboard but disabled it, taking over all of its functions.

- i486 OverDrive (P23T/P24T): i486SX, i486SX2, i486DX2 or i486DX4. Marked as upgrade processors, some models had different pinouts or voltage handling abilities from "standard" chips of the same speed stepping. Fitted to a coprocessor or "OverDrive" socket on the motherboard, worked the same as the i487SX.

The specified maximum internal clock frequency (on Intel's versions) ranged from 16 to 100 MHz. The 16 MHz i486SX model was used by Dell Computers.

One of the few 80486 models specified for a 50 MHz bus (486DX-50) initially had overheating problems and was moved to the 0.8 micrometre fabrication process. However, problems continued when the 486DX-50 was installed in local bus systems due to the high bus speed, making it rather unpopular with mainstream consumers as local bus video was considered a requirement at the time, though it remained popular with users of EISA systems. The 486DX-50 was soon eclipsed by the clock-doubled i486DX2 which instead ran the CPU logic at twice the external bus speed which actually means it was slower due to the bus running at only 25 or 33 MHz

More powerful 80486 iterations such as the OverDrive and DX4 were less popular (the latter available as an OEM part only), as they came out after Intel had released the next generation P5 Pentium processor family. Certain steppings of the DX4 also officially supported 50 MHz bus operation but was a seldom used feature.

| Model | Specified max clock | Voltage | L1-Cache | Introduced | Notes | |

|---|---|---|---|---|---|---|

| i486DX (P4) | 20, 25 MHz 33 MHz 50 MHz | 5 V | 8 KB WT | April 1989 May 1990 June 1991 | The original chip (without any clock doubling) |

| i486SL | 20, 25, 33 MHz | 5 V or 3.3 V | 8 KB WT | November 1992 | Low power version of the i486DX, reduced VCore, SMM (System Management Mode), stop clock, and power saving features – mainly for use in portable computers |

| i486SX (P23) | 16, 20, 25 MHz 33 MHz | 5 V | 8 KB WT | September 1991 September 1992 | An i486DX with the FPU part disabled or missing. Early variants were parts with disabled (defective) FPUs.[4] Later versions had the FPU removed from the die to reduce area and hence cost. |

| i486DX2 (P24) | 40/20, 50/25 MHz 66/33 MHz | 5 V | 8 KB WT | March 1992 August 1992 | The internal processor clock runs at twice the clock rate of the external bus clock |

| i486DX-S (P4S) | 33 MHz; 50 MHz | 5 V or 3.3 V | 8 KB WT | June 1993 | SL Enhanced 486DX | |

| i486DX2-S (P24S) | 40/20, 50/25 MHz (66/33 MHz) | 5 V or 3.3 V | 8 KB WT | June 1993 | |

| i486SX-S (P23S) | 25, 33 MHz | 5 V or 3.3 V | 8 KB WT | June 1993 | SL Enhanced 486SX |

| i486SX2 | 50/25, 66/33 MHz | 5 V | 8 KB WT | March 1994 | i486DX2 with the FPU disabled |

| IntelDX4 (P24C) | 75/25, 100/33 MHz | 3.3 V | 16 KB WT | March 1994 | Designed to run at triple clock rate (not quadruple as often believed; the DX3, which was meant to run at 2.5× the clock speed, was never released). DX4 models that featured write-back cache were identified by an "&EW" laser etched into their top surface, while the write-through models were identified by "&E". |

| IntelDX4WB | 100/33 MHz | 3.3 V | 16 KB WB | October 1994 | |

| i486DX2WB (P24D) | 50/25, 66/33 MHz | 5 V | 8 KB WB | October 1994 | ||

| i486DX2 (P24LM) | 90/30 MHz; 100/33 MHz | 2.5–2.9 V | 8 KB WT | 1994 | ||

| i486GX | up to 33 MHz | 3.3 V | 8 KB WT | Embedded Ultra-Low power CPU with all features of the i486SX and 16 bit external data bus. This CPU is for embedded battery-operated and hand-held applications. |

WT = Write-Through cache strategy, WB = Write-Back cache strategy

Other makers of 80486-like CPUs

80486 compatible processors have been produced by other companies such as IBM, Texas Instruments, AMD, Cyrix, UMC, and SGS Thompson. Some were clones (identical at the microarchitectural level), others were clean room implementations of the Intel instruction-set. (IBM's multiple source requirement is one of the reasons behind its x86-manufacturing since the 80286.) The 80486 was, however, covered by many of Intel's patents covering new R&D as well as that of the prior 80386. Intel and IBM have broad cross-licenses of these patents, and AMD was granted rights to the relevant patents in the 1995 settlement of a lawsuit between the companies.[5]

AMD produced several clones of the 80486 using a 40 MHz bus (486DX-40, 486DX/2-80, and 486DX/4-120) which had no equivalent available from Intel, as well as a part specified for 90 MHz, using a 30 MHz external clock, that was sold only to OEMs. The fastest running 80486 CPU, the Am5x86, ran at 133 MHz and was released by AMD in 1995. 150 MHz and 160 MHz parts were planned but never officially released.

Cyrix made a variety of 80486-compatible processors, positioned at the cost-sensitive desktop and low-power (laptop) markets. Unlike AMD's 80486 clones, the Cyrix processors were the result of clean-room reverse-engineering. Cyrix's early offerings included the 486DLC and 486SLC, two hybrid chips which plugged into 386DX or SX sockets respectively, and offered 1 KB of cache (versus 8 KB for the then-current Intel/AMD parts). Cyrix also made "real" 80486 processors, which plugged into the i486's socket and offered 2 or 8 KB of cache. Clock-for-clock, the Cyrix-made chips were generally slower than their Intel/AMD equivalents, though later products with 8 KB caches were more competitive, if late to market.

The Motorola 68040 (e.g. used in the Macintosh Quadra series), while not compatible with the 80486, was often positioned as the 80486's equivalent in features and performance. Clock-for-clock basis the Motorola 68040 could significantly outperform the Intel 80486 chip.[6][7] However, the 80486 had the ability to be clocked significantly faster without suffering from overheating problems. The Motorola 68040 performance lagged behind the later production 80486 systems.

Motherboards and buses

Early 80486 machines were equipped with several ISA slots (using an emulated PC/AT-bus) and sometimes one or two 8-bit–only slots (compatible with the PC/XT-bus).[lower-alpha 3] Many motherboards enabled overclocking of these up from the default 6 or 8 MHz to perhaps 16.7 or 20 MHz (half the i486 bus clock) in a number of steps, often from within the BIOS setup. Especially older peripheral cards normally worked well at such speeds as they often used standard MSI chips instead of slower (at the time) custom VLSI designs. This could give significant performance gains (such as for old video cards moved from a 386 or 286 computer, for example). However, operation beyond 8 or 10 MHz could sometimes lead to stability problems, at least in systems equipped with SCSI or sound cards.

Some motherboards came equipped with a 32-bit bus called EISA that was backward compatible with the ISA-standard. EISA offered a number of attractive features such as increased bandwidth, extended addressing, IRQ sharing, and card configuration through software (rather than through jumpers, DIP switches, etc.) However, EISA cards were expensive and therefore mostly employed in servers and workstations. Consumer desktops often used the simpler but faster VESA Local Bus (VLB), unfortunately somewhat prone to electrical and timing-based instability; typical consumer desktops had ISA slots combined with a single VLB slot for a video card. VLB was gradually replaced by PCI during the final years of the 80486 period. Few Pentium class motherboards had VLB support as VLB was based directly on the i486 bus; it was no trivial matter adapting it to the quite different P5 Pentium-bus. ISA persisted through the P5 Pentium generation and was not completely displaced by PCI until the Pentium III era.

Late 80486 boards were normally equipped with both PCI and ISA slots, and sometimes a single VLB slot as well. In this configuration VLB or PCI throughput suffered depending on how buses were bridged. Initially, the VLB slot in these systems was usually fully compatible only with video cards (quite fitting as "VESA" stands for Video Electronics Standards Association); VLB-IDE, multi I/O, or SCSI cards could have problems on motherboards with PCI slots. The VL-Bus operated at the same clock speed as the i486-bus (basically being a local 80486-bus) while the PCI bus also usually depended on the i486 clock but sometimes had a divider setting available via the BIOS. This could be set to 1/1 or 1/2, sometimes even 2/3 (for 50 MHz CPU clocks). Some motherboards limited the PCI clock to the specified maximum of 33 MHz and certain network cards depended on this frequency for correct bit-rates. The ISA clock was typically generated by a divider of the CPU/VLB/PCI clock (as implied above).

One of the earliest complete systems to use the 80486 chip was the Apricot VX FT, produced by United Kingdom hardware manufacturer Apricot Computers. Even overseas in the United States it was popularised as "The World's First 80486" in the September 1989 issue of Byte magazine (shown right).

Later 80486 boards also supported Plug-And-Play, a specification designed by Microsoft that began as a part of Windows 95 to make component installation easier for consumers.

Gaming

The 486DX2 66 MHz processor was popular on home-oriented PCs during the early to mid 1990s, toward the end of the MS-DOS gaming era. It was often coupled with a VESA Local Bus video card.

The introduction of 3D computer graphics spelled the end of the 80486's reign, because 3D graphics make heavy use of floating point calculations and require a faster CPU cache and more memory bandwidth. Developers began to target the P5 Pentium processor family almost exclusively with x86 assembly language optimizations (e.g., Quake) which led to the usage of terms like "Pentium compatible processor" for software requirements. Many of these games required the speed of the P5 Pentium processor family's double-pipelined architecture.

Obsolescence

The AMD Am5x86, up to 133 MHz, and Cyrix Cx5x86, up to 120 MHz, were the last 80486 processors that were often used in late generation 80486 motherboards with PCI slots and 72-pin SIMMs that are designed to be able to run Windows 95, and also often used as upgrades for older 80486 motherboards. While the Cyrix Cx5x86 faded quite quickly when the Cyrix 6x86 took over, the AMD Am5x86 was important during the time when the AMD K5 was delayed.

In the general purpose desktop computer role, 80486-based machines remained in use into the early-2000s, especially as Windows 95, Windows 98, and Windows NT 4.0 were the latest Microsoft operating systems to officially support installation on a 80486-based system.[8][9] However, as Windows 95/98 and Windows NT 4.0 were eventually overtaken by newer operating systems, 80486 systems likewise fell out of use. Still, a number of 80486 machines have remained in use today, mostly for backward compatibility with older programs (most notably games), especially since many of them have problems running on newer operating systems. However, DOSBox is also available for current operating systems and provides emulation of the 80486 instruction set, as well as full compatibility with most DOS-based programs.[10]

Although the 80486 was eventually overtaken by the Pentium for personal computer applications, Intel had continued production for use in embedded systems. In May 2006 Intel announced that production of the 80486 would stop at the end of September 2007.[11]

See also

- List of Intel microprocessors

- Motorola 68040, although not compatible, was often positioned as the Motorola equivalent to the Intel 80486 in terms of performance and features.

Notes

- ↑ The 386, 286, and even the 8086 all had overlapping fetch, decode, execution (calculation), and write back; however, tightly pipelined usually means that all stages perform their respective duties within the same length time slot. In contrast loosely pipelined implies that some kind of buffering is used to decouple the units and allow them to work more independently. Both the original 8086 and the x86-chips of today are "loosely pipelined" in this sense, while the 80486 and the original Pentium worked in a "tightly pipelined" manner for typical instructions. This included most "CISC" type instructions as well as the simple load/store-free "RISC-like" ones, although the most complex also used some dedicated microcode control.

- ↑ The "low-end" 16 and 25 MHz 80486 parts did not use a clock multiplier and are therefore comparable to a 386/286 clock by clock.

- ↑ In general, 8-bit ISA slots in these systems were implemented just by leaving off the shorter "C"/"D" connector of the slot, though the copper traces for a 16-bit slot were still there on the motherboard; the computer could tell no difference between an 8-bit ISA adapter in such a slot and the same adapter in a 16-bit slot, and there were still enough 8-bit adapters in circulation that vendors figured they could save money on a few connectors this way. Also, leaving off the 16-bit extension to the ISA connector allowed use of some early 8-bit ISA cards that otherwise could not be used due to the PCB "skirt" hanging down into that 16-bit extension space. IBM was the first to do this in the IBM AT.

References

- 1 2 3 Intel (July 1997). Embedded Intel486 Processor Hardware Reference Manual (273025-001).

- ↑ 486 32-bit CPU breaks new ground in chip density and operating performance. (Intel Corp.) (product announcement) EDN | May 11, 1989 | Pryce, Dave

- ↑ Lewis, Peter H. (October 22, 1989). "THE EXECUTIVE COMPUTER; The Race to Market a 80486 Machine". The New York Times. Retrieved May 5, 2010.

- ↑ Newnes 8086 Family Pocket Book – Ian Sinclair (ISBN 0 4349 1872 5)

- ↑ "AMD–Intel Litigation History". AMD. Retrieved 20 May 2012.

- ↑ "CISC: The Intel 80486 vs. The Motorola MC68040". July 1992. Retrieved 20 May 2013.

- ↑ 68040 Microprocessor Archived February 16, 2012, at the Wayback Machine.

- ↑ "Minimum Hardware Requirements for a Windows 98 Installation". 24 January 2001. Archived from the original on 2004-12-05.

- ↑ "Windows NT 4.0 Workstation" (in German). WinHistory.de.

- ↑ "System Requirements". DOSBox.com.

- ↑ Tony Smith (18 May 2006). "Intel cashes in ancient chips. i386, i486, i960 finally for the chop". HARDWARE. Retrieved 20 May 2012.

This article is based on material taken from the Free On-line Dictionary of Computing prior to 1 November 2008 and incorporated under the "relicensing" terms of the GFDL, version 1.3 or later.

External links

- Intel486 datasheets

- Intel 80486 images and descriptions at cpu-collection.de

- Die photo of Intel 486DX