Floating-gate MOSFET

The floating-gate MOSFET (FGMOS) is a field-effect transistor, whose structure is similar to a conventional MOSFET. The gate of the FGMOS is electrically isolated, creating a floating node in DC, and a number of secondary gates or inputs are deposited above the floating gate (FG) and are electrically isolated from it. These inputs are only capacitively connected to the FG. Since the FG is completely surrounded by highly resistive material, the charge contained in it remains unchanged for long periods of time. Usually Fowler-Nordheim tunneling and hot-carrier injection mechanisms are used to modify the amount of charge stored in the FG.

Some applications of the FGMOS are digital storage element in EPROM, EEPROM and flash memories, neuronal computational element in neural networks, analog storage element, digital potentiometers and single-transistor DACs.

History

The first report of a floating-gate MOSFET was made by Kahng and Sze,[1] and dates back to 1967. The first application of the FGMOS was to store digital data in EEPROM, EPROM and flash memories. However, the current interest in FGMOS circuits started from developing large-scale computations in neuromorphic systems, which are inherently analog.

In 1989 Intel employed the FGMOS as an analog nonvolatile memory element in its ETANN chip,[2] demonstrating the potential of using FGMOS devices for applications other than digital memory.

Three research accomplishments laid the groundwork for much of the current FGMOS circuit development:

- Thomsen and Brooke's demonstration and use of electron tunneling in a standard CMOS double-poly process[3] allowed many researchers to investigate FGMOS circuits concepts without requiring access to specialized fabrication processes.

- The νMOS, or neuron-MOS, circuit approach by Shibata and Ohmi[4] provided the initial inspiration and framework to use capacitors for linear computations. These researchers concentrated on the FG circuit properties instead of the device properties, and used either UV light to equalize charge, or simulated FG elements by opening and closing MOSFET switches.

- Carver Mead's adaptive retina[5] gave the first example of using continuously-operating FG programming/erasing techniques, in this case UV light, as the backbone of an adaptive circuit technology.

Structure

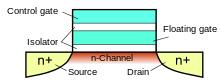

An FGMOS can be fabricated by electrically isolating the gate of a standard MOS transistor, so that there are no resistive connections to its gate. A number of secondary gates or inputs are then deposited above the floating gate (FG) and are electrically isolated from it. These inputs are only capacitively connected to the FG, since the FG is completely surrounded by highly resistive material. So, in terms of its DC operating point, the FG is a floating node.

For applications where the charge of the FG needs to be modified, a pair of small extra transistors are added to each FGMOS transistor to conduct the injection and tunneling operations. The gates of every transistor are connected together; the tunneling transistor has its source, drain and bulk terminals interconnected to create a capacitive tunneling structure. The injection transistor is connected normally and specific voltages are applied to create hot carriers that are then injected via an electric field into the floating gate.

FGMOS transistor for purely capacitive use can be fabricated on N or P versions. For charge modification applications, the tunneling transistor (and therefore the operating FGMOS) needs to be embedded into a well, hence the technology dictates the type of FGMOS that can be fabricated.

Modeling

Large signal DC

The equations modeling the DC operation of the FGMOS can be derived from the equations that describe the operation of the MOS transistor used to build the FGMOS. If it is possible to determine the voltage at the FG of an FGMOS device, it is then possible to express its drain to source current using standard MOS transistor models. Therefore, to derive a set of equations that model the large signal operation of an FGMOS device, it is necessary to find the relationship between its effective input voltages and the voltage at its FG.

Small signal

An N-input FGMOS device has N−1 more terminals than a MOS transistor, and therefore, N+2 small signal parameters can be defined: N effective input transconductances, an output transconductance and a bulk transconductance. Respectively:

where is the total capacitance seen by the floating gate. These equations show two drawbacks of the FGMOS compared with the MOS transistor:

- Reduction of the input transconductance

- Reduction of the output resistance

Simulation

Under normal conditions, a floating node in a circuit represents an error because its initial condition is unknown unless it is somehow fixed. This generates two problems: first, it is not straightforward to simulate these circuits; and second, an unknown amount of charge might stay trapped at the floating gate during the fabrication process which will result in an unknown initial condition for the FG voltage.

Among the many solutions proposed for the computer simulation, one of the most promising methods is an Initial Transient Analysis (ITA) proposed by Rodriguez-Villegas,[6] where the FGs are set to zero volts or a previously known voltage based on the measurement of the charge trapped in the FG after the fabrication process. A transient analysis is then run with the supply voltages set to their final values, letting the outputs evolve normally. The values of the FGs can then be extracted and used for posterior small-signal simulations, connecting a voltage supply with the initial FG value to the floating gate using a very-high-value inductor.

Applications

The usage and applications of the FGMOS can be broadly classified in two cases. If the charge in the floating gate is not modified during the circuit usage, the operation is capacitively coupled.

In the capacitively coupled regime of operation, the net charge in the floating gate is not modified. Examples of application for this regime are single transistor adders, DACs, multipliers and logic functions, variable threshold inverters,

Using the FGMOS as a programmable charge element, it is commonly used for non-volatile storage such as flash, EPROM and EEPROM memory. In this context, floating-gate MOSFETs are useful because of their ability to store an electrical charge for extended periods of time without a connection to a power supply. Other applications of the FGMOS are neuronal computational element in neural networks, analog storage element and e-pots.

See also

References

- ↑ D. Kahng and S.M. Sze, "A floating-gate and its application to memory devices," The Bell System Technical Journal, vol. 46, no. 4, 1967, pp. 1288-1295

- ↑ M. Holler, S. Tam, H. Castro, and R. Benson, "An electrically trainable artificial neural network with 10240 'floating gate' synapses," Proceeding of the International Joint Conference on Neural Networks, Washington, D.C., vol. II, 1989, pp. 191-196

- ↑ A. Thomsen and M.A. Brooke, "A floating-gate MOSFET with tunneling injector fabricated using a standard double-polysilicon CMOS process," IEEE Electron Device Letters, vol. 12, 1991, pp. 111-113

- ↑ T. Shibata and T. Ohmi, "A functional MOS transistor featuring gate-level weighted sum and threshold operations," IEEE Transactions on Electron Devices, vol. 39, no. 6, 1992, pp. 1444-1455

- ↑ C.A. Mead and M. Ismail, editors, Analog VLSI Implementation of Neural Systems, Kluwer Academic Publishers, Norwell, MA, 1989

- ↑ Rodriguez-Villegas, Esther. Low Power and Low Voltage Circuit Design with the FGMOS Transistor

External links

- EXPLOITING FLOATING-GATE TRANSISTOR PROPERTIES IN ANALOG AND MIXED-SIGNAL CIRCUIT DESIGN

- Howstuffworks "How ROM Works"

- Floating Gate Devices

- FLOATING-GATE TRANSISTORS IN ANALOG AND MIXED-SIGNAL CIRCUIT DESIGN

- Tunable and reconfigurable circuits using floating-gate transistors