Memristor

| Type | Passive |

|---|---|

| Working principle | Memristance |

| Invented | Leon Chua (1971) |

| First production | HP Labs (2008) |

| Electronic symbol | |

|

| |

| Computer memory types |

|---|

| Volatile |

| RAM |

|

In development |

| Historical |

|

| Non-volatile |

| ROM |

| NVRAM |

| Early stage NVRAM |

| Mechanical |

| In development |

| Historical |

|

The memristor (/ˈmɛmrᵻstər/; a portmanteau of memory resistor) was a term coined in 1971 by circuit theorist Leon Chua as a missing non-linear passive two-terminal electrical component relating electric charge and magnetic flux linkage.[1] The operation of RRAM devices was recently connected to the memristor concept.[2] According to the characterizing mathematical relations, the memristor would hypothetically operate in the following way. The memristor's electrical resistance is not constant but depends on the history of current that had previously flowed through the device, i.e., its present resistance depends on how much electric charge has flowed in what direction through it in the past. The device remembers its history—the so-called non-volatility property.[3] When the electric power supply is turned off, the memristor remembers its most recent resistance until it is turned on again.[4][5]

Leon Chua has more recently argued that the definition could be generalized to cover all forms of two-terminal non-volatile memory devices based on resistance switching effects.[3] However, some experimental evidence contradicts this claim since a non-passive nanobattery effect is observable in resistance switching memory.[6] Chua also argued that the memristor is the oldest known circuit element, with its effects predating the resistor, capacitor and inductor.[7]

In 2008, a team at HP Labs claimed to have found Chua's missing memristor based on an analysis of a thin film of titanium dioxide;[8] the HP result was published in Nature.[4] The memristor is currently under development by various teams including Hewlett-Packard, SK Hynix, HRL Laboratories and Knowm Inc.

These devices are intended for applications in nanoelectronic memories, computer logic and neuromorphic/neuromemristive computer architectures.[9] Commercial availability of memristor memory has been estimated as 2018.[10] In March 2012, a team of researchers from HRL Laboratories and the University of Michigan announced the first functioning memristor array built on a CMOS chip.[11]

Background

In his 1971 paper, Chua extrapolated a conceptual symmetry between the nonlinear resistor (voltage vs. current), nonlinear capacitor (voltage vs. charge) and nonlinear inductor (magnetic flux linkage vs. current). He then inferred the possibility of a memristor as another fundamental nonlinear circuit element linking magnetic flux and charge. In contrast to a linear (or nonlinear) resistor the memristor has a dynamic relationship between current and voltage including a memory of past voltages or currents. Other scientists had proposed dynamic memory resistors such as the memistor of Bernard Widrow, but Chua attempted to introduce mathematical generality.

Memristor resistance depends on the integral of the input applied to the terminals (rather than on the instantaneous value of the input as in a varistor).[4] Since the element "remembers" the amount of current that last passed through, it was tagged by Chua with the name "memristor". Another way of describing a memristor is as any passive two-terminal circuit element that maintains a functional relationship between the time integral of current (called charge) and the time integral of voltage (often called flux, as it is related to magnetic flux). The slope of this function is called the memristance M and is similar to variable resistance.

The memristor definition is based solely on the fundamental circuit variables of current and voltage and their time-integrals, just like the resistor, capacitor and inductor. Unlike those three elements however, which are allowed in linear time-invariant or LTI system theory, memristors of interest have a dynamic function with memory and may be described as some function of net charge. There is no such thing as a standard memristor. Instead, each device implements a particular function, wherein the integral of voltage determines the integral of current, and vice versa. A linear time-invariant memristor, with a constant value for M, is simply a conventional resistor.[1] Manufactured devices are never purely memristors (ideal memristor), but also exhibit some capacitance and resistance.

Memristor definition and criticism

According to the original 1971 definition, the memristor was the fourth fundamental circuit element, forming a non-linear relationship between electric charge and magnetic flux linkage. In 2011 Chua argued for a broader definition that included all 2-terminal non-volatile memory devices based on resistance switching.[3] Williams argued that MRAM, phase change memory and RRAM were memristor technologies.[14] Some researchers argued that biological structures such as blood[15] and skin[16] fit the definition. Others argued that the memory device under development by HP Labs and other forms of RRAM were not memristors but rather part of a broader class of variable resistance systems[17] and that a broader definition of memristor is a scientifically unjustifiable land grab that favored HP's memristor patents.[18]

In 2011, Meuffels and Schroeder noted that one of the early memristor papers included a mistaken assumption regarding ionic conduction.[19] In 2012, Meuffels and Soni discussed some fundamental issues and problems in the realization of memristors.[20] They indicated inadequacies in the electrochemical modelling presented in the Nature paper "The missing memristor found"[4] because the impact of concentration polarization effects on the behavior of metal−TiO2-x−metal structures under voltage or current stress was not considered. This critique was referred to by Valov et al.[6] in 2013.

Meuffels and Soni[20] furthermore noted that the dynamic state equations set up for a solely current-controlled memristor with the so-called non-volatility property[3] would allow the violation of Landauer's principle of the minimum amount of energy required to change "information" states in a system: In order to exhibit the non-volatility property requires "that the internal memristor or “information” states are separated from each other by Gibbs free energy barriers",[20] viz. there is always a lower limit of energy requirement for changing a bit value in a binary device.[21] This critique was adopted by Di Ventra and Pershin[22] in 2013. The concept of a solely current-controlled memristor provides no physical mechanism enabling such a memristor system to cope with inevitable thermal fluctuations,[20] viz. such a system would erratically change its state just under the influence of white current noise.[23] Memristors whose resistance (memory) states depend solely on the current or voltage history would thus be unable to protect their memory states against unavoidable Johnson–Nyquist noise and permanently suffer from information loss, a so-called "stochastic catastrophe",[22] viz. such envisioned memristors cannot exist as solid state devices in physical reality.

Other researchers noted that memristor models based on the assumption of linear ionic drift do not account for asymmetry between set time (high-to-low resistance switching) and reset time (low-to-high resistance switching) and do not provide ionic mobility values consistent with experimental data. Non-linear ionic drift models have been proposed to compensate for this deficiency.[24]

A 2014 article from researchers of ReRAM concluded that Strukov’s (HP's) initial/basic memristor modelling equations do not reflect the actual device physics well, whereas subsequent (physics-based) models such as Pickett’s model or Menzel’s ECM model (Menzel is a co-author of this paper) have adequate predictability but are computationally prohibitive. As of 2014, the search continues for a model that balances these issues; the article identifies Chang’s and Yakopcic’s models as potentially good compromises.[25]

Martin Reynolds, an electrical engineering analyst with research outfit Gartner, commented that while HP was being sloppy in calling their device a memristor, critics were being pedantic in saying it was not a memristor.[26]

In the article "The Missing Memristor has Not been Found," published on Scientific Reports in 2015 by Vongehr and Meng,[27] it has been shown that the real memristor defined in 1971 is not possible without using magnetic induction. This has been illustrated by constructing a mechanical analog of the memristor and then analytically showing that the mechanical memristor can not be constructed without using an inertial mass. As it is well known that the mechanical equivalent of an electrical inductor is mass, it proves that memristors are not possible without using magnetic induction. Thus, it can be argued that the variable resistance devices, such as the RRAMs, and the conceptual memristors may have no equivalence at all.[27][28]

Experimental tests for memristors

Chua suggested experimental tests to determine if a device may properly be categorized as a memristor:[29]

- The Lissajous curve in the voltage-current plane is a pinched hysteresis loop when driven by any bipolar periodic voltage or current without respect to initial conditions.

- The area of each lobe of the pinched hysteresis loop shrinks as the frequency of the forcing signal increases.

- As the frequency tends to infinity, the hysteresis loop degenerates to a straight line through the origin, whose slope depends on the amplitude and shape of the forcing signal.

According to Chua[30][31] all resistive switching memories including ReRAM, MRAM and phase change memory meet these criteria and are memristors. However, the lack of data for the Lissajous curves over a range of initial conditions or over a range of frequencies, complicates assessments of this claim.

Experimental evidence shows that redox-based resistance memory (ReRAM) includes a nanobattery effect that is contrary to Chua's memristor model. This indicates that the memristor theory needs to be extended or corrected to enable accurate ReRAM modeling.[6]

Theory

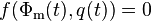

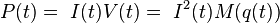

The memristor was originally defined in terms of a non-linear functional relationship between magnetic flux linkage Φm(t) and the amount of electric charge that has flowed, q(t):[1]

The magnetic flux linkage, Φm, is generalized from the circuit characteristic of an inductor. It does not represent a magnetic field here. Its physical meaning is discussed below. The symbol Φm may be regarded as the integral of voltage over time.[32]

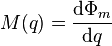

In the relationship between Φm and q, the derivative of one with respect to the other depends on the value of one or the other, and so each memristor is characterized by its memristance function describing the charge-dependent rate of change of flux with charge.

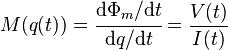

Substituting the flux as the time integral of the voltage, and charge as the time integral of current, the more convenient form is

To relate the memristor to the resistor, capacitor, and inductor, it is helpful to isolate the term M(q), which characterizes the device, and write it as a differential equation.

| Device | Characteristic property (units) | Differential equation |

|---|---|---|

| Resistor (R) | Resistance (V / A, or ohm, Ω) | R = dV / dI |

| Capacitor (C) | Capacitance (C / V, or farad) | C = dq / dV |

| Inductor (L) | Inductance (Wb / A, or henry) | L = dΦm / dI |

| Memristor (M) | Memristance (Wb / C, or ohm) | M = dΦm / dq |

The above table covers all meaningful ratios of differentials of I, Q, Φm, and V. No device can relate dI to dq, or dΦm to dV, because I is the derivative of Q and Φm is the integral of V.

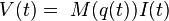

It can be inferred from this that memristance is charge-dependent resistance. If M(q(t)) is a constant, then we obtain Ohm's Law R(t) = V(t)/ I(t). If M(q(t)) is nontrivial, however, the equation is not equivalent because q(t) and M(q(t)) can vary with time. Solving for voltage as a function of time produces

This equation reveals that memristance defines a linear relationship between current and voltage, as long as M does not vary with charge. Nonzero current implies time varying charge. Alternating current, however, may reveal the linear dependence in circuit operation by inducing a measurable voltage without net charge movement—as long as the maximum change in q does not cause much change in M.

Furthermore, the memristor is static if no current is applied. If I(t) = 0, we find V(t) = 0 and M(t) is constant. This is the essence of the memory effect.

The power consumption characteristic recalls that of a resistor, I2R.

As long as M(q(t)) varies little, such as under alternating current, the memristor will appear as a constant resistor. If M(q(t)) increases rapidly, however, current and power consumption will quickly stop.

M(q) is physically restricted to be positive for all values of q (assuming the device is passive and does not become superconductive at some q). A negative value would mean that it would perpetually supply energy when operated with alternating current.

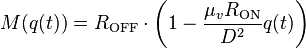

In 2008 researchers from HP Labs introduced a model for a memristance function based on thin films of titanium dioxide.[4] For RON ≪ ROFF the memristance function was determined to be

where ROFF represents the high resistance state, RON represents the low resistance state, μv represents the mobility of dopants in the thin film, and D represents the film thickness. The HP Labs group noted that "window functions" were necessary to compensate for differences between experimental measurements and their memristor model due to nonlinear ionic drift and boundary effects.

Operation as a switch

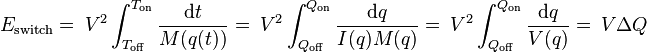

For some memristors, applied current or voltage causes substantial change in resistance. Such devices may be characterized as switches by investigating the time and energy that must be spent to achieve a desired change in resistance. This assumes that the applied voltage remains constant. Solving for energy dissipation during a single switching event reveals that for a memristor to switch from Ron to Roff in time Ton to Toff, the charge must change by ΔQ = Qon−Qoff.

Substituting V=I(q)M(q), and then ∫dq/V = ∆Q/V for constant VTo produces the final expression. This power characteristic differs fundamentally from that of a metal oxide semiconductor transistor, which is capacitor-based. Unlike the transistor, the final state of the memristor in terms of charge does not depend on bias voltage.

The type of memristor described by Williams ceases to be ideal after switching over its entire resistance range, creating hysteresis, also called the "hard-switching regime".[4] Another kind of switch would have a cyclic M(q) so that each off-on event would be followed by an on-off event under constant bias. Such a device would act as a memristor under all conditions, but would be less practical.

Memristive systems

The memristor was generalized to memristive systems in Chua's 1976 paper.[29] Whereas a memristor has mathematically scalar state, a system has vector state. The number of state variables is independent of the number of terminals.

Chua applied this model to empirically-observed phenomena, including the Hodgkin–Huxley model of the axon and a thermistor at constant ambient temperature. He also described memristive systems in terms of energy storage and easily observed electrical characteristics. These characteristics might match resistive random-access memory relating the theory to active areas of research.

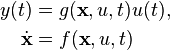

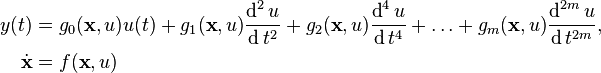

In the more general concept of an n-th order memristive system the defining equations are

where u(t) is an input signal, y(t) is an output signal, the vector x represents a set of n state variables describing the device, and g and f are continuous functions. For a current-controlled memristive system the signal u(t) represents the current signal i(t) and the signal y(t) represents the voltage signal v(t). For a voltage-controlled memristive system the signal u(t) represents the voltage signal v(t) and the signal y(t) represents the current signal i(t).

The pure memristor is a particular case of these equations, namely when x depends only on charge (x=q) and since the charge is related to the current via the time derivative dq/dt=i(t). Thus for pure memristors f (i.e. the rate of change of the state) must be equal or proportional to the current i(t) .

Pinched hysteresis

One of the resulting properties of memristors and memristive systems is the existence of a pinched hysteresis effect.[33] For a current-controlled memristive system, the input u(t) is the current i(t), the output y(t) is the voltage v(t), and the slope of the curve represents the electrical resistance. The change in slope of the pinched hysteresis curves demonstrates switching between different resistance states which is a phenomenon central to ReRAM and other forms of two-terminal resistance memory. At high frequencies, memristive theory predicts the pinched hysteresis effect will degenerate, resulting in a straight line representative of a linear resistor. It has been proven that some types of non-crossing pinched hysteresis curves (denoted Type-II) cannot be described by memristors.[34]

Extended memristive systems

Some researchers have raised the question of the scientific legitimacy of HP's memristor models in explaining the behavior of ReRAM.[17][18] and have suggested extended memristive models to remedy perceived deficiencies.[6]

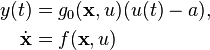

One example[35] attempts to extend the memristive systems framework by including dynamic systems incorporating higher-order derivatives of the input signal u(t) as a series expansion

where m is a positive integer, u(t) is an input signal, y(t) is an output signal, the vector x represents a set of n state variables describing the device, and the functions g and f are continuous functions. This equation produces the same zero-crossing hysteresis curves as memristive systems but with a different frequency response than that predicted by memristive systems.

Another example suggests including an offset value a to account for an observed nanobattery effect which violates the predicted zero-crossing pinched hysteresis effect.[6]

Implementations

Titanium dioxide memristor

Interest in the memristor revived when an experimental solid state version was reported by R. Stanley Williams of Hewlett Packard in 2007.[36][37][38] The article was the first to demonstrate that a solid-state device could have the characteristics of a memristor based on the behavior of nanoscale thin films. The device neither uses magnetic flux as the theoretical memristor suggested, nor stores charge as a capacitor does, but instead achieves a resistance dependent on the history of current.

Although not cited in HP's initial reports on their TiO2 memristor, the resistance switching characteristics of titanium dioxide were originally described in the 1960s.[39]

The HP device is composed of a thin (50 nm) titanium dioxide film between two 5 nm thick electrodes, one titanium, the other platinum. Initially, there are two layers to the titanium dioxide film, one of which has a slight depletion of oxygen atoms. The oxygen vacancies act as charge carriers, meaning that the depleted layer has a much lower resistance than the non-depleted layer. When an electric field is applied, the oxygen vacancies drift (see Fast ion conductor), changing the boundary between the high-resistance and low-resistance layers. Thus the resistance of the film as a whole is dependent on how much charge has been passed through it in a particular direction, which is reversible by changing the direction of current.[4] Since the HP device displays fast ion conduction at nanoscale, it is considered a nanoionic device.[40]

Memristance is displayed only when both the doped layer and depleted layer contribute to resistance. When enough charge has passed through the memristor that the ions can no longer move, the device enters hysteresis. It ceases to integrate q=∫Idt, but rather keeps q at an upper bound and M fixed, thus acting as a constant resistor until current is reversed.

Memory applications of thin-film oxides had been an area of active investigation for some time. IBM published an article in 2000 regarding structures similar to that described by Williams.[41] Samsung has a U.S. patent for oxide-vacancy based switches similar to that described by Williams.[42] Williams also has a U.S. patent application related to the memristor construction.[43]

In April 2010, HP labs announced that they had practical memristors working at 1 ns (~1 GHz) switching times and 3 nm by 3 nm sizes,[44] which bodes well for the future of the technology.[45] At these densities it could easily rival the current sub-25 nm flash memory technology.

Polymeric memristor

In 2004, Krieger and Spitzer described dynamic doping of polymer and inorganic dielectric-like materials that improved the switching characteristics and retention required to create functioning nonvolatile memory cells.[46] They used a passive layer between electrode and active thin films, which enhanced the extraction of ions from the electrode. It is possible to use fast ion conductor as this passive layer, which allows a significant reduction of the ionic extraction field.

In July 2008, Erokhin and Fontana claimed to have developed a polymeric memristor before the more recently announced titanium dioxide memristor.[47]

In 2010, Alibart, Gamrat, Vuillaume et al.[48] introduced a new hybrid organic/nanoparticle device (the NOMFET : Nanoparticle Organic Memory Field Effect Transistor), which behaves as a memristor [49] and which exhibits the main behavior of a biological spiking synapse.This device, also called synapstor (synapse transistor), was used to demonstrate a neuro-inspired circuit (associative memory showing a pavlovian learning) [50]

In 2012, Crupi, Pradhan and Tozer described a proof of concept design to create neural synaptic memory circuits using organic ion-based memristors.[51] The synapse circuit demonstrated long-term potentiation for learning as well as inactivity based forgetting. Using a grid of circuits, a pattern of light was stored and later recalled. This mimics the behavior of the V1 neurons in the primary visual cortex that act as spatiotemporal filters that process visual signals such as edges and moving lines.

Layered memristor

In 2014, Bessonov et al. reported a flexible memristive device comprising a MoOx/MoS2 heterostructure sandwiched between silver electrodes on a plastic foil.[52] The fabrication method is entirely based on printing and solution-processing technologies using two-dimensional layered transition metal dichalcogenides (TMDs). The memristors are mechanically flexible, optically transparent and produced at low cost. The memristive behaviour of switches was found to be accompanied by a prominent memcapacitive effect. High switching performance, demonstrated synaptic plasticity and sustainability to mechanical deformations promise to emulate the appealing characteristics of biological neural systems in novel computing technologies.

Ferroelectric memristor

The ferroelectric memristor[53] is based on a thin ferroelectric barrier sandwiched between two metallic electrodes. Switching the polarization of the ferroelectric material by applying a positive or negative voltage across the junction can lead to a two order of magnitude resistance variation: ROFF ≫ RON (an effect called Tunnel Electro-Resistance). In general, the polarization does not switch abruptly. The reversal occurs gradually through the nucleation and growth of ferroelectric domains with opposite polarization. During this process, the resistance is neither RON or ROFF, but in between. When the voltage is cycled, the ferroelectric domain configuration evolves, allowing a fine tuning of the resistance value. The ferroelectric memristor's main advantages are that ferroelectric domain dynamics can be tuned, offering a way to engineer the memristor response, and that the resistance variations are due to purely electronic phenomena, aiding device reliability, as no deep change to the material structure is involved.

Spin memristive systems

Spintronic memristor

Chen and Wang, researchers at disk-drive manufacturer Seagate Technology described three examples of possible magnetic memristors.[54] In one device resistance occurs when the spin of electrons in one section of the device points in a different direction from those in another section, creating a "domain wall", a boundary between the two sections. Electrons flowing into the device have a certain spin, which alters the device's magnetization state. Changing the magnetization, in turn, moves the domain wall and changes the resistance. The work's significance led to an interview by IEEE Spectrum.[55] A first experimental proof of the spintronic memristor based on domain wall motion by spin currents in a magnetic tunnel junction was given in 2011.[56]

Memristance in a magnetic tunnel junction

The magnetic tunnel junction has been proposed to act as a memristor through several potentially complementary mechanisms, both extrinsic (redox reactions, charge trapping/detrapping and electromigration within the barrier) and intrinsic (spin-transfer torque).

Extrinsic Mechanism

Based on research performed between 1999 and 2003, Bowen et al. published experiments in 2006 on a magnetic tunnel junction (MTJ) endowed with bi-stable spin-dependent states[57](resistive switching). The MTJ consists in a SrTiO3 (STO) tunnel barrier that separates half-metallic oxide LSMO and ferromagnetic metal CoCr electrodes. The MTJ's usual two device resistance states, characterized by a parallel or antiparallel alignment of electrode magnetization, are altered by applying an electric field. When the electric field is applied from the CoCr to the LSMO electrode, the tunnel magnetoresistance (TMR) ratio is positive. When the direction of electric field is reversed, the TMR is negative. In both cases, large amplitudes of TMR on the order of 30% are found. Since a fully spin-polarized current flows from the half-metallic LSMO electrode, within the Julliere model, this sign change suggests a sign change in the effective spin polarization of the STO/CoCr interface. The origin to this multistate effect lies with the observed migration of Cr into the barrier and its state of oxidation. The sign change of TMR can originate from modifications to the STO/CoCr interface density of states, as well as from changes to the tunneling landscape at the STO/CoCr interface induced by CrOx redox reactions.

Reports on MgO-based memristive switching within MgO-based MTJs appeared starting in 2008[58] and 2009.[59] While the drift of oxygen vacancies within the insulating MgO layer has been proposed to describe the observed memristive effects,[59] another explanation could be charge trapping/detrapping on the localized states of oxygen vacancies[60] and its impact[61] on spintronics. This highlights the importance of understanding what role oxygen vacancies play in the memristive operation of devices that deploy complex oxides with an intrinsic property such as ferroelectricity[62] or multiferroicity.[63]

Intrinsic Mechanism

The magnetization state of a MTJ can be controlled by Spin-transfer torque, and can thus, through this intrinsic physical mechanism, exhibit memristive behavior. This spin torque is induced by current flowing through the junction, and leads to an efficient means of achieving a MRAM. However, the length of time the current flows through the junction determines the amount of current needed, i.e., charge is the key variable.[64]

The combination of intrinsic (spin-transfer torque) and extrinsic (resistive switching) mechanisms naturally leads to a second-order memristive system described by the state vector x = (x1,x2), where x1 describes the magnetic state of the electrodes and x2 denotes the resistive state of the MgO barrier. In this case the change of x1 is current-controlled (spin torque is due to a high current density) whereas the change of x2 is voltage-controlled (the drift of oxygen vacancies is due to high electric fields). The presence of both effects in a memristive magnetic tunnel junction led to the idea of a nanoscopic synapse-neuron system.[65]

Spin memristive system

A fundamentally different mechanism for memristive behavior has been proposed by Pershin[66] and Di Ventra.[67][68] The authors show that certain types of semiconductor spintronic structures belong to a broad class of memristive systems as defined by Chua and Kang.[29] The mechanism of memristive behavior in such structures is based entirely on the electron spin degree of freedom which allows for a more convenient control than the ionic transport in nanostructures. When an external control parameter (such as voltage) is changed, the adjustment of electron spin polarization is delayed because of the diffusion and relaxation processes causing hysteresis. This result was anticipated in the study of spin extraction at semiconductor/ferromagnet interfaces,[69] but was not described in terms of memristive behavior. On a short time scale, these structures behave almost as an ideal memristor.[1] This result broadens the possible range of applications of semiconductor spintronics and makes a step forward in future practical applications.

Applications

Williams' solid-state memristors can be combined into devices called crossbar latches, which could replace transistors in future computers, given their much higher circuit density.

They can potentially be fashioned into non-volatile solid-state memory, which would allow greater data density than hard drives with access times similar to DRAM, replacing both components.[13] HP prototyped a crossbar latch memory that can fit 100 gigabits in a square centimeter,[8] and proposed a scalable 3D design (consisting of up to 1000 layers or 1 petabit per cm3).[70] In May 2008 HP reported that its device reaches currently about one-tenth the speed of DRAM.[71] The devices' resistance would be read with alternating current so that the stored value would not be affected.[72] In May 2012 it was reported that access time had been improved to 90 nanoseconds if not faster, approximately one hundred times faster than contemporaneous flash memory, while using one percent as much energy.[73]

Memristor patents include applications in programmable logic,[74] signal processing,[75] neural networks,[76] control systems,[77] reconfigurable computing,[78] brain-computer interfaces[79] and RFID.[80] Memristive devices are potentially used for stateful logic implication, allowing a replacement for CMOS-based logic computation. Several early works in this direction are reported.[81] [82]

In 2009, a simple electronic circuit[83] consisting of an LC network and a memristor was used to model experiments on adaptive behavior of unicellular organisms.[84] It was shown that subjected to a train of periodic pulses, the circuit learns and anticipates the next pulse similar to the behavior of slime molds Physarum polycephalum where the viscosity of channels in the cytoplasm responds to periodic environment changes.[84] Applications of such circuits may include, e.g., pattern recognition. The DARPA SyNAPSE project funded HP Labs, in collaboration with the Boston University Neuromorphics Lab, has been developing neuromorphic architectures which may be based on memristive systems. In 2010, Versace and Chandler described the MoNETA (Modular Neural Exploring Traveling Agent) model.[85] MoNETA is the first large-scale neural network model to implement whole-brain circuits to power a virtual and robotic agent using memristive hardware.[86] Application of the memristor crossbar structure in the construction of an analog soft computing system was demonstrated by Merrikh-Bayat and Shouraki.[87] In 2011 they showed[88] how memristor crossbars can be combined with fuzzy logic to create an analog memristive neuro-fuzzy computing system with fuzzy input and output terminals. Learning is based on the creation of fuzzy relations inspired from Hebbian learning rule.

In 2013 Leon Chua published a tutorial underlining the broad span of complex phenomena and applications that memristors span and how they can be used as non-volatile analog memories and can mimic classic habituation and learning phenomena.[89]

Memcapacitors and meminductors

In 2009, Di Ventra, Pershin and Chua extended[90] the notion of memristive systems to capacitive and inductive elements in the form of memcapacitors and meminductors, whose properties depend on the state and history of the system, further extended in 2013 by Di Ventra and Pershin.[22]

Memfractance and memfractor, 2nd and 3rd order memristor, memcapacitor and meminductor

In September 2014, Mohamed-Salah Abdelouahab, Rene Lozi and Leon Chua, published a general theory of 1st, 2nd, 3rd order and nth order memristive element using fractional derivatives.[91]

Timeline

1808

Sir Humphry Davy is claimed by Leon Chua to have performed the first experiments showing the effects of a memristor.[7][92]

1960

Bernard Widrow coins the term memistor (i.e. memory resistor) to describe components of an early artificial neural network called ADALINE.

1965

Cognitronics Corp are granted a patent, number US3359521, for "Bistable resistance memory device"

1968

Argall publishes an article showing the resistance switching effects of TiO2 which was later claimed in 2008 to be evidence of a memristor by researchers from Hewlett Packard.[39]

1971

Leon Chua postulated a new two-terminal circuit element characterized by a relationship between charge and flux linkage as a fourth fundamental circuit element.[1]

1976

Chua and his student Sung Mo Kang generalized the theory of memristors and memristive systems including a property of zero crossing in the Lissajous curve characterizing current vs. voltage behavior.[29]

2008

On May 1 Strukov, Snider, Stewart and Williams published an article in Nature identifying a link between the 2-terminal resistance switching behavior found in nanoscale systems and memristors.[93]

On August 10, Dr. Kris Campbell discloses a new approach to developing, fabricating, and testing memristors on top of CMOS chips.[94]

2009

On January 23 Di Ventra, Pershin and Chua extended the notion of memristive systems to capacitive and inductive elements, namely capacitors and inductors whose properties depend on the state and history of the system.[90]

On May 1 Kim, et al. described a newly discovered memristor material based on magnetite nanoparticles and proposed an extended memristor model including both time-dependent resistance and time-dependent capacitance.[95]

On July 13 Mouttet described a memristor-based pattern recognition circuit performing an analog variation of the exclusive nor function. The circuit architecture was proposed as a way to circumvent Von Neumann architecture#Von Neumann bottleneck for processors used in robotic control systems.[96]

On August 4 Choi et al. described the physical realization of an electrically modifiable array of memristive neural synapses.[97]

2010

On April 8 Borghetti, et al. described an array of memristors demonstrated the ability to perform logical operations.[98]

On April 20 Memristor-based content addressable memory (MCAM) was introduced.[99]

On June 1 Mouttet argued that the interpretation of the memristor as a fourth fundamental was incorrect and that the HP Labs device was part of a broader class of memristive systems.[100]

On August 31 HP announced they had teamed up with Hynix to produce a commercial product dubbed "ReRam".[101]

On December 7 So and Koo developed a hydrogel form of memristor that was speculated to be useful to construct a brain-computer interface.[102]

2011

In October Tse demonstrated printed memristive counters based on solution processing, with potential applications as low-cost packaging components (no battery needed; powered by energy scavenging mechanism).[103] In October 2011, HP claimed that the commercial availability of memristor technology was 18 months away.[104]

2012

On March 23 HRL Laboratories and the University of Michigan announced the first functioning memristor array built on a CMOS chip for applications in neuromorphic computer architectures.[11]

On July 5, Italian researchers from Politecnico di Torino, Alon Ascoli and Fernando Corinto, showed that a purely passive circuit, employing already-existing components, can exhibit memristive dynamics.[105] The circuit is composed of an elementary diode bridge and an RLC series circuit, introducing nonlinearity and dynamical behaviour into the system, respectively. In his latest classification of memristive systems, dated September 2013, Prof. L. O. Chua classified this circuit as an example of a generalized memristor.

On July 31, Meuffels and Soni[20] questioned the applicability of the concept of a solely current-controlled, non-volatile memristor to any physically realizable device.

2013

On February 27 Thomas et al., demonstrated that a memristor can be used to mimic a synapse more readily than traditional CMOS technology and be used as the foundation for building physical circuits capable of learning. The approach utilizes memristors as key components in a blueprint for an artificial brain.[106]

On April 23 Valov, et al., argued that the current memristive theory must be extended to a whole new theory to properly describe redox-based resistively switching elements (ReRAM). The main reason is the existence of nanobatteries in redox-based resistive switches which violates the memristor theory's requirement for a pinched hysteresis.[6]

2014

On February 10, Nugent and Molter presented a new form of computing dubbed "AHaH Computing", which uses differential pairs of memristors as the storage medium for synaptic weights. The proposed architecture provides a solution to the "von Neumann bottleneck" by merging processor and memory, and future hardware based on the technology may reduce the power consumption of machine learning applications.[107]

On November 10, Bessonov et al. demonstrated a new type of flexible memristors comprising solution-processed MoOx/MoS2 heterostructures stacked with printed silver electrodes on a plastic foil.[52]

2015

On 6 April, Sangwan et al. reported first study of memristive phenomena within atomically thin single layer MoS2 devices. [108]

On June 25, Vongehr and Meng published an article with the title "The Missing Memristor has Not been Found," in Scientific Reports clarifying that the originally hypothesized real memristor device is missing and likely impossible. The argument has been illustrated by finding an ideal mechanical memristor element and purely mechanical memristive systems, and hypothesizing a real mechanical memristor device that requires inert mass just like the 1971 implied device requires magnetic induction.[27]

See also

References

- 1 2 3 4 5 Chua, L. O. (1971), "Memristor—The Missing Circuit Element", IEEE Transactions on Circuit Theory, CT-18 (5): 507–519, doi:10.1109/TCT.1971.1083337

- ↑ Strukov, D. B.; Snide, G. S.; Stewart, D. R.; Williams, R. S. (2008). "The missing memristor found". Nature 453: 80–83. doi:10.1038/nature06932. PMID 18451858.

- 1 2 3 4 Chua, L. O. (2011), "Resistance switching memories are memristors", Applied Physics A 102 (4): 765–783, Bibcode:2011ApPhA.102..765C, doi:10.1007/s00339-011-6264-9

- 1 2 3 4 5 6 7 Strukov, D. B.; Snider, G. S.; Stewart, D. R.; Williams, S. R. (2008), "The missing memristor found", Nature 453 (7191): 80–83, Bibcode:2008Natur.453...80S, doi:10.1038/nature06932, PMID 18451858

- ↑ Memristor FAQ, Hewlett-Packard, retrieved 2010-09-03

- 1 2 3 4 5 6 Valov, I.; et al. (2013), "Nanobatteries in redox-based resistive switches require extension of memristor theory", Nature Communications 4 (4): 1771, arXiv:1303.2589, Bibcode:2013NatCo...4E1771V, doi:10.1038/ncomms2784, PMC 3644102, PMID 23612312

- 1 2 Clarke, P. (23 May 2012), "Memristor is 200 years old, say academics", EE Times, retrieved 2012-05-25

- 1 2 Johnson, R. C. (30 April 2008), "'Missing link' memristor created", EE Times, retrieved 2008-04-30

- ↑ Marks, P. (30 April 2008), "Engineers find 'missing link' of electronics", New Scientist, retrieved 2008-04-30

- ↑ HP 100TB Memristor drives by 2018 – if you're lucky, admits tech titan, 1 November 2013

- 1 2 Artificial synapses could lead to advanced computer memory and machines that mimic biological brains, HRL Laboratories, March 23, 2012, retrieved March 30, 2012

- ↑ Bush, S. (2 May 2008), "HP nano device implements memristor", Electronics Weekly

- 1 2 Kanellos, M. (30 April 2008), "HP makes memory from a once theoretical circuit", CNET News, retrieved 2008-04-30

- ↑ Mellor, C. (10 October 2011), "HP and Hynix to produce the memristor goods by 2013", The Register, retrieved 2012-03-07

- ↑ Courtland, R. (1 April 2011), "Memristors...Made of Blood?", IEEE Spectrum, retrieved 2012-03-07

- ↑ McAlpine, K. (2 March 2011), "Sweat ducts make skin a memristor", New Scientist, retrieved 2012-03-07

- 1 2 Clarke, P. (16 January 2012), "Memristor brouhaha bubbles under", EETimes, retrieved 2012-03-02

- 1 2 Marks, P. (23 February 2012), "Online spat over who joins memristor club", New Scientist, retrieved 2012-03-19

- ↑ Meuffels, P.; Schroeder, H. (2011), "Comment on "Exponential ionic drift: fast switching and low volatility of thin-film memristors" by D.B. Strukov and R.S. Williams in Appl. Phys. A (2009) 94: 515-519", Applied Physics A 105: 65–67, Bibcode:2011ApPhA.105...65M, doi:10.1007/s00339-011-6578-7

- 1 2 3 4 5 Meuffels, P.; Soni, R. (2012). "Fundamental Issues and Problems in the Realization of Memristors". arXiv:1207.7319 [cond-mat.mes-hall].

- ↑ Kish, L. B.; Granqvist, C. G. (2014). "DEMONS: MAXWELL’S DEMON, SZILARD’S ENGINE AND LANDAUER’S ERASURE–DISSIPATION". arXiv:1412.2166 [physics.gen-ph].

- 1 2 3 Di Ventra, M.; Pershin, Y. V. (2013), "On the physical properties of memristive, memcapacitive and meminductive systems", Nanotechnology 24 (25): 255201, arXiv:1302.7063, Bibcode:2013Nanot..24y5201D, doi:10.1088/0957-4484/24/25/255201, PMID 23708238

- ↑ Slipko, V. A.; Pershin, Y. V.; Di Ventra, M. (2013), "Changing the state of a memristive system with white noise", Physical Review E 87: 042103, arXiv:1209.4103, Bibcode:2013PhRvE..87a2103L, doi:10.1103/PhysRevE.87.012103

- ↑ Hashem, N.; Das, S. (2012), "Switching-time analysis of binary-oxide memristors via a non-linear model" (PDF), Applied Physics Letters 100 (26): 262106, Bibcode:2012ApPhL.100z2106H, doi:10.1063/1.4726421, retrieved 2012-08-09

- ↑ Linn, E.; Siemon, A.; Waser, R.; Menzel, S. (23 March 2014). "Applicability of Well-Established Memristive Models for Simulations of Resistive Switching Devices". Circuits and Systems I: Regular Papers, IEEE Transactions on 61 (8): 2402–2410. arXiv:1403.5801. doi:10.1109/TCSI.2014.2332261.

- ↑ Garling, C. (25 July 2012), "Wonks question HP's claim to computer-memory missing link", Wired.com, retrieved 2012-09-23

- 1 2 3 Vongehr, S.; Meng, X. (2015), "The Missing Memristor has Not been Found", Scientific Reports 5: 11657, doi:10.1038/srep11657

- ↑ Vongehr, S. (21 Mar 2015), Purely Mechanical Memristors and the Missing Memristor, arXiv:1504.00300

- 1 2 3 4 Chua, L. O.; Kang, S. M. (1 January 1976), "Memristive devices and systems", Proceedings of the IEEE 64 (2): 209–223, doi:10.1109/PROC.1976.10092

- ↑ Chua, L. (13 June 2012), Memristors: Past, Present and future (PDF), retrieved 2013-01-12

- ↑ Adhikari, S. P.; Sah, M. P.; Hyongsuk, K.; Chua, L. O. (2013), "Three Fingerprints of Memristor", IEEE Transactions on Circuits and Systems I 60 (11): 3008–3021, doi:10.1109/TCSI.2013.2256171

- ↑ Knoepfel, H. (1970), Pulsed high magnetic fields, New York: North-Holland, p. 37, Eq. (2.80)

- ↑ Pershin, Y. V.; Di Ventra, M. (2011), "Memory effects in complex materials and nanoscale systems", Advances in Physics 60 (2): 145–227, arXiv:1011.3053, Bibcode:2011AdPhy..60..145P, doi:10.1080/00018732.2010.544961

- ↑ Biolek, D.; Biolek, Z.; Biolkova, V. (2011), "Pinched hysteresis loops of ideal memristors, memcapacitors and meminductors must be 'self-crossing'", Electronics Letters 47 (25): 1385–1387, doi:10.1049/el.2011.2913

- ↑ Mouttet, B. (2012). "Memresistors and non-memristive zero-crossing hysteresis curves". arXiv:1201.2626 [cond-mat.mes-hall].

- ↑ Fildes, J. (13 November 2007), Getting More from Moore's Law, BBC News, retrieved 2008-04-30

- ↑ Taylor, A. G. (2007), "Nanotechnology in the Northwest" (PDF), Bulletin for Electrical and Electronic Engineers of Oregon 51 (1): 1

- ↑ Stanley Williams, HP Labs, retrieved 2011-03-20

- 1 2 Argall, F. (1968), "Switching Phenomena in Titanium Oxide Thin Films", Solid-State Electronics 11 (5): 535–541, Bibcode:1968SSEle..11..535A, doi:10.1016/0038-1101(68)90092-0

- ↑ Terabe, K.; Hasegawa, T.; Liang, C.; Aono, M. (2007), "Control of local ion transport to create unique functional nanodevices based on ionic conductors", Science and Technology of Advanced Materials 8 (6): 536–542, Bibcode:2007STAdM...8..536T, doi:10.1016/j.stam.2007.08.002

- ↑ Beck, A.; et al. (2000), "Reproducible switching effect in thin oxide films for memory applications", Applied Physics Letters 77: 139, Bibcode:2000ApPhL..77..139B, doi:10.1063/1.126902

- ↑ US Patent 7,417,271

- ↑ US Patent Application 11/542,986

- ↑ Finding the Missing Memristor - R. Stanley Williams

- ↑ Markoff, J. (7 April 2010), "H.P. Sees a Revolution in Memory Chip", New York Times

- ↑ Krieger, J. H.; Spitzer, S. M. (2004), "Non-traditional, Non-volatile Memory Based on Switching and Retention Phenomena in Polymeric Thin Films", Proceedings of the 2004 Non-Volatile Memory Technology Symposium, IEEE, p. 121, doi:10.1109/NVMT.2004.1380823, ISBN 0-7803-8726-0

- ↑ Erokhin, V.; Fontana, M. P. (2008). "Electrochemically controlled polymeric device: A memristor (and more) found two years ago". arXiv:0807.0333 [cond-mat.soft].

- ↑ An organic-nanoparticle transistor behaving as a biological spiking synapse. F. Alibart, S. Pleutin, D. Guerin, C. Novembre, S. Lenfant, K. Lmimouni, C. Gamrat & D. Vuillaume. Adv. Func. Mater. 20(2), 330-337 (2010). Adv. Func. Mater.

- ↑ A memristive nanoparticle/organic hybrid synapstor for neuro-inspired computing. F. Alibart, S. Pleutin, O. Bichler, C. Gamrat, T. Serrano-Gotarredona, B. Linares-Barranco & D. Vuillaume. Adv. Func. Mater. 22, 609-616 (2012). Adv. Func. Mater.

- ↑ Pavlov's Dog Associative Learning Demonstrated on Synaptic-like Organic Transistors. O. Bichler, W. Zhao, F. Alibart, S. Pleutin, S. Lenfant, D. Vuillaume & C. Gamrat. Neural Computation 25(2), 549-566 (2013). Neural Computation

- ↑ Crupi, M.; Pradhan, L.; Tozer, S. (2012), "Modelling Neural Plasticity with Memristors" (PDF), IEEE Canadian Review 68: 10–14

- 1 2 Bessonov, A. A.; et al. (2014), "Layered memristive and memcapacitive switches for printable electronics", Nature Materials 14: 199–204, Bibcode:2015NatMa..14..199B, doi:10.1038/nmat4135, PMID 25384168

- ↑ Chanthbouala, A.; et al. (2012), "A ferroelectric memristor", Nature Materials 11 (10): 860–864, arXiv:1206.3397, Bibcode:2012NatMa..11..860C, doi:10.1038/nmat3415

- ↑ Wang, X.; Chen, Y.; Xi, H.; Dimitrov, D. (2009), "Spintronic Memristor through Spin Torque Induced Magnetization Motion", IEEE Electron Device Letters 30 (3): 294–297, Bibcode:2009IEDL...30..294W, doi:10.1109/LED.2008.2012270

- ↑ Savage, N. (2009), "Spintronic Memristor", IEEE Spectrum, retrieved 2011-03-20

- ↑ Chanthbouala, A.; et al. (2011), "Vertical-current-induced domain-wall motion in MgO-based magnetic tunnel junctions with low current densities", Nature Physics 7: 626–630, arXiv:1102.2106, Bibcode:2011NatPh...7..626C, doi:10.1038/nphys1968

- ↑ Bowen, M.; Maurice, J.-L.; Barthe´le´my, A.; Prod’homme, P.; Jacquet, E.; Contour, J.-P.; Imhoff, D.; Colliex, C. (2006). "Bias-crafted magnetic tunnel junctions with bistable spin-dependent states". Applied Physics Letters 89 (10): 103517. Bibcode:2006ApPhL..89j3517B. doi:10.1063/1.2345592. ISSN 0003-6951. Retrieved 2014-12-15.

- ↑ Halley, D.; Majjad, H.; Bowen, M.; Najjari, N.; Henry, Y.; Ulhaq-Bouillet, C.; Weber, W.; Bertoni, G.; Verbeeck, J.; Van Tendeloo, G. (2008). "Electrical switching in Fe/Cr/MgO/Fe magnetic tunnel junctions". Applied Physics Letters 92 (21): 212115. Bibcode:2008ApPhL..92u2115H. doi:10.1063/1.2938696. ISSN 0003-6951. Retrieved 2014-12-15.

- 1 2 Krzysteczko, P.; Günter, R.; Thomas, A. (2009), "Memristive switching of MgO based magnetic tunnel junctions", Applied Physics Letters 95 (11): 112508, arXiv:0907.3684, Bibcode:2009ApPhL..95k2508K, doi:10.1063/1.3224193

- ↑ Bertin, Eric; Halley, David; Henry, Yves; Najjari, Nabil; Majjad, Hicham; Bowen, Martin; DaCosta, Victor; Arabski, Jacek; Doudin, Bernard (2011), "Random barrier double-well model for resistive switching in tunnel barriers", Journal of Applied Physics 109 (8): 083712, Bibcode:2011JAP...109a3712D, doi:10.1063/1.3530610, retrieved 2014-12-15

- ↑ Schleicher, F.; Halisdemir, U.; Lacour, D.; Gallart, M.; Boukari, S.; Schmerber, G.; Davesne, V.; Panissod, P.; Halley, D.; Majjad, H.; Henry, Y.; Leconte, B.; Boulard, A.; Spor, D.; Beyer, N.; Kieber, C.; Sternitzky, E.; Cregut, O.; Ziegler, M.; Montaigne, F.; Beaurepaire, E.; Gilliot, P.; Hehn, M.; Bowen, M. (2014-08-04), "Localized states in advanced dielectrics from the vantage of spin- and symmetry-polarized tunnelling across MgO", Nature Communications 5, Bibcode:2014NatCo...5E4547S, doi:10.1038/ncomms5547, ISSN 2041-1723, retrieved 2014-12-15

- ↑ Garcia, V.; Bibes, M.; Bocher, L.; Valencia, S.; Kronast, F.; Crassous, A.; Moya, X.; Enouz-Vedrenne, S.; Gloter, A.; Imhoff, D.; Deranlot, C.; Mathur, N. D.; Fusil, S.; Bouzehouane, K.; Barthelemy, A. (2010-02-26), "Ferroelectric Control of Spin Polarization", Science 327 (5969): 1106–1110, Bibcode:2010Sci...327.1106G, doi:10.1126/science.1184028, ISSN 0036-8075, retrieved 2014-12-17

- ↑ Pantel, D.; Goetze, S.; Hesse, D.; Alexe, M. (2012-02-26), "Reversible electrical switching of spin polarization in multiferroic tunnel junctions", Nature Materials 11 (4): 289–293, Bibcode:2012NatMa..11..289P, doi:10.1038/nmat3254, ISSN 1476-1122, retrieved 2014-12-17

- ↑ Huai, Y. (2008), "Spin-Transfer Torque MRAM (STT-MRAM): Challenges and Prospects" (PDF), AAPPS Bulletin 18 (6): 33

- ↑ Krzysteczko, P.; Münchenberger, J.; Schäfers, M.; Reiss, G.; Thomas, A. (2012), "The Memristive Magnetic Tunnel Junction as a Nanoscopic Synapse-Neuron System", Advanced Materials 24 (6): 762–766, doi:10.1002/adma.201103723

- ↑ Yuriy V. Pershin

- ↑ Massimiliano Di Ventra

- ↑ Pershin, Y. V.; Di Ventra, M. (2008), "Spin memristive systems: Spin memory effects in semiconductor spintronics", Physical Review B 78 (11): 113309, arXiv:0806.2151, Bibcode:2008PhRvB..78k3309P, doi:10.1103/PhysRevB.78.113309

- ↑ Pershin, Y. V.; Di Ventra, M. (2008), "Current-voltage characteristics of semiconductor/ferromagnet junctions in the spin-blockade regime", Physical Review B 77 (7): 073301, arXiv:0707.4475, Bibcode:2008PhRvB..77g3301P, doi:10.1103/PhysRevB.77.073301

- ↑ Finding the Missing Memristor - R. Stanley Williams

- ↑ Markoff, J. (1 May 2008), "H.P. Reports Big Advance in Memory Chip Design", New York Times, retrieved 2008-05-01

- ↑ Gutmann, E. (1 May 2008), "Maintaining Moore's law with new memristor circuits", Ars Technica, retrieved 2008-05-01

- ↑ Palmer, J. (18 May 2012), Memristors in silicon promising for dense, fast memory, BBC News, retrieved 2012-05-18

- ↑ U.S. Patent 7,203,789

- ↑ U.S. Patent 7,302,513

- ↑ U.S. Patent 7,359,888

- ↑ U.S. Patent 7,609,086

- ↑ U.S. Patent 7,902,857

- ↑ U.S. Patent 7,902,867

- ↑ U.S. Patent 8,113,437

- ↑ Lehtonen, E. (2010), "Two memristors suffice to compute all Boolean functions" (PDF), Electronics Letters 46 (3): 239–240, doi:10.1049/el.2010.3407

- ↑ Chattopadhyay, A.; Rakosi, Z. (2011), "2011 IEEE/IFIP 19th International Conference on VLSI and System-on-Chip", VLSI-SoC, p. 200, doi:10.1109/VLSISoC.2011.6081665, ISBN 978-1-4577-0170-2

|chapter=ignored (help) - ↑ Pershin, Y. V.; La Fontaine, S.; Di Ventra, M. (2009), "Memristive model of amoeba learning", Physical Review E 80 (2): 021926, arXiv:0810.4179, Bibcode:2009PhRvE..80b1926P, doi:10.1103/PhysRevE.80.021926

- 1 2 Saigusa, T.; Tero, A.; Nakagaki, T.; Kuramoto, Y. (2008), "Amoebae Anticipate Periodic Events", Physical Review Letters 100 (1): 018101, Bibcode:2008PhRvL.100a8101S, doi:10.1103/PhysRevLett.100.018101, PMID 18232821

- ↑ Versace, M.; Chandler, B. (2010), "MoNETA: A Mind Made from Memristors", IEEE Spectrum 12 (12): 30–37, doi:10.1109/MSPEC.2010.5644776

- ↑ Snider, G.; et al. (2011), "From Synapses to Circuitry: Using Memristive Memory to Explore the Electronic Brain", IEEE Computer 44 (2): 21–28, doi:10.1109/MC.2011.48

- ↑ Merrikh-Bayat, F.; Bagheri-Shouraki, S.; Rohani, A. (2011), "Memristor crossbar-based hardware implementation of IDS method", IEEE Transactions on Fuzzy Systems 19 (6): 1083–1096, doi:10.1109/TFUZZ.2011.2160024

- ↑ Merrikh-Bayat, F.; Bagheri-Shouraki, S. (2011). "Efficient neuro-fuzzy system and its Memristor Crossbar-based Hardware Implementation". arXiv:1103.1156 [cs.AI].

- ↑ Chua, L. (2013). "Memristor, Hodgkin-Huxley, and Edge of Chaos". Nanotechnology 24 (38): 383001. Bibcode:2013Nanot..24L3001C. doi:10.1088/0957-4484/24/38/383001.

- 1 2 Di Ventra, M.; Pershin, Y. V.; Chua, L. (2009), "Circuit elements with memory: memristors, memcapacitors and meminductors", Proceedings of the IEEE 97 (10): 1717–1724, arXiv:0901.3682, doi:10.1109/JPROC.2009.2021077

- ↑ Abdelhouahad, M.-S.; Lozi, R.; Chua, L. (September 2014), "Memfractance: A Mathematical Paradigm for Circuit Elements with Memory", International Journal of Bifurcation and Chaos 24 (9): 1430023 (29 pages), Bibcode:2014IJBC...2430023A, doi:10.1142/S0218127414300237

- ↑ Prodromakis, T.; Toumazou, C.; Chua, L. (June 2012), "Two centuries of memristors", Nature Materials 11 (6): 478–481, Bibcode:2012NatMa..11..478P, doi:10.1038/nmat3338, PMID 22614504

- ↑ Strukov, D. B.; Snider, G. S.; Stewart, D. R.; Williams, R. S. (2008), "The missing memristor found", Nature 453 (7191): 80–83, Bibcode:2008Natur.453...80S, doi:10.1038/nature06932, PMID 18451858

- ↑ http://ieeexplore.ieee.org/xpl/login.jsp?tp=&arnumber=4616863&url=http%3A%2F%2Fieeexplore.ieee.org%2Fxpls%2Fabs_all.jsp%3Farnumber%3D4616863

- ↑ Kim, T.H.; et al. (2009), "Nanoparticle Assemblies as Memristors", Nano Letters 9 (6): 2229–2233, Bibcode:2009NanoL...9.2229K, doi:10.1021/nl900030n

- ↑ Mouttet, B. (2009), "Memristor Pattern Recognition Circuit Architecture for Robotics", Proceedings of the 2nd International Multi-Conference on Engineering and Technological Innovation 2, pp. 65–70

- ↑ Choi, H.; et al. (2009), "An electrically modifiable synapse array of resistive switching memory", Nanotechnology 20 (34): 345201, Bibcode:2009Nanot..20H5201C, doi:10.1088/0957-4484/20/34/345201, PMID 19652272

- ↑ Borghetti, J.; Snider, G. S.; Kuekes, P. J.; Yang, J. J.; Stewart, D. R.; Williams, R. S. (2010), "'Memristive' switches enable 'stateful' logic operations via material implication", Nature 464 (7290): 873–6, Bibcode:2010Natur.464..873B, doi:10.1038/nature08940, PMID 20376145

- ↑ Eshraghian, K.; Rok Cho, K. R.; Kavehei, O.; Kang, S. K.; Abbott, D.; Kang, S. M. (2010), "Memristor MOS Content Addressable Memory (MCAM): Hybrid Architecture for Future High Performance Search Engines", IEEE Transactions on Very Large Scale Integration (VLSI) Systems 1005: 3687, arXiv:1005.3687, Bibcode:2010arXiv1005.3687E, doi:10.1109/TVLSI.2010.2049867

- ↑ Mouttet, B. (2010), The mythology of the memristor, ISCAS, Paris, France

- ↑ HP and Hynix to popularize new kind of chip circuit dubbed "memristor", Reuters, September 1, 2010

- ↑ "Chemists Construct Squishy Memristors and Diodes", IEEE Spectrum, December 7, 2010

- ↑ "Solution-Processed Memristive Junctions Used in a Threshold Indicator", IEEE Transactions on Electronic Devices 58, Oct 2011: 3435–3443, Bibcode:2011ITED...58.3435N, doi:10.1109/TED.2011.2162334

- ↑ HP to replace flash and SSD in 2013, 7 October 2011

- ↑ Corinto, F.; Ascoli, A. (2012), "Memristive diode bridge with LCR filter", Electronics Letters 48 (14): 824–825, doi:10.1049/el.2012.1480

- ↑ "Memristor that "learns" provides blueprint for artificial brain", R&D magazine, Feb 2012

- ↑ Nugent, M. A.; Molter, T. W. (2014). "AHaH Computing–From Metastable Switches to Attractors to Machine Learning". PLoS ONE 9: e85175. Bibcode:2014PLoSO...985175N. doi:10.1371/journal.pone.0085175.

- ↑ Sangwan, V. K.; Jariwala, D.; Kim, I. S.; Shen, K.-S.; Marks, T. J.; Lauhon, L. J.; Hersam, M. C. (2015), "Gate-tunable memristive phenomena mediated by grain boundaries in single-layer MoS2", Nature Nanotechnology 10: 403–406, doi:10.1038/nnano.2015.56

Further reading

- Ronald Tetzlaff, ed. (2013). Memristors and Memristive Systems. Springer. ISBN 978-1-4614-9068-5.

- Andrew Adamatzky and Leon Chua, eds. (2013). Memristor Networks. Springer. ISBN 978-3-319-02630-5.

- Keith Atkin (2013), "An introduction to the memristor", Phys. Educ. 48 317 doi:10.1088/0031-9120/48/3/317. One of the relatively simple experiments described in this paper has been reproduced by Chris Winstead.

- Muthuswamy, B et al., "Memristor Modelling", IEEE ISCAS 2014, doi:10.1109/ISCAS.2014.6865179; see also accompanying video/

External links

| Wikimedia Commons has media related to Memristors. |

- Finding the missing memristor on YouTube

- Interactive database of memristor papers (2013)

- Simonite, Tom (April 21, 2015). "Machine Dreams". Technology Review. Retrieved April 2015.

| ||||||||||||||||||||||||||||||||||||||

|