IBM System/360 Model 67

| Designer | IBM |

|---|---|

| Bits | 32-bit |

| Introduced | 1967 |

| Design | CISC |

| Type | Register-Register, Register-Memory, Memory-Memory |

| Encoding | Variable (2, 4, or 6 bytes long) |

| Branching | Condition code |

| Endianness | Big |

| Page size | 4 KB byte pages |

| Extensions | Dynamic Address Translation (DAT), 24 or 32-bit addresses, memory reference and change bits |

| Registers | |

| General purpose | 16× 32-bit |

| Floating point | 4× 64-bit |

The IBM System/360 Model 67 (S/360-67) was an important IBM mainframe model in the late 1960s.[1] Unlike the rest of the S/360 series, it included features to facilitate time-sharing applications, notably a DAT box to support virtual memory and 32-bit addressing. The S/360-67 was otherwise compatible with the rest of the S/360 series.

Origins

The S/360-67 was intended to satisfy the needs of key time-sharing customers, notably MIT (where Project MAC had become a notorious IBM sales failure), the University of Michigan, General Motors, Bell Labs, Princeton University, and the Carnegie Institute of Technology (later Carnegie Mellon University).[2]

In the mid-1960s a number of organizations were interested in offering interactive computing services using time-sharing.[3] At that time the work that computers could perform was limited by their lack of real memory storage capacity. When IBM introduced its System/360 family of computers in the mid-1960s, it did not provide a solution for this limitation and within IBM there were conflicting views about the importance of and need to support time-sharing.

A paper titled Program and Addressing Structure in a Time-Sharing Environment by Bruce Arden, Bernard Galler, Frank Westervelt (all associate directors at UM's academic Computing Center), and Tom O'Brian building upon some basic ideas developed at the Massachusetts Institute of Technology (MIT) was published in January 1966.[4] The paper outlined a virtual memory architecture using dynamic address translation (DAT) that could be used to implement time-sharing.

After a year of negotiations and design studies, IBM agreed to make a one-of-a-kind version of its S/360-65 mainframe computer for the University of Michigan. The S/360-65M[3] would include dynamic address translation (DAT) features that would support virtual memory and allow support for time-sharing. Initially IBM decided not to supply a time-sharing operating system for the new machine.

As other organizations heard about the project they were intrigued by the time-sharing idea and expressed interest in ordering the modified IBM S/360 series machines. With this demonstrated interest IBM changed the computer's model number to S/360-67 and made it a supported product. When IBM realized there was a market for time-sharing, it agreed to develop a new time-sharing operating system called TSS/360 (TSS stood for Time-sharing System) for delivery at roughly the same time as the first model S/360-67.

The first S/360-67 was shipped in May 1966. The S/360-67 was withdrawn on March 15, 1977.[5]

Before the announcement of the Model 67, IBM had announced models 64 and 66, DAT versions of its 60 and 62 models, but they were almost immediately replaced by the 67 at the same time that the 60 and 62 were replaced by the 65.[6]

Announcement

IBM announced the S/360-67 in its August 16, 1965 "blue letters" (a standard mechanism used by IBM to make product announcements). IBM stated that:[7]

- "Special bid restrictions have been removed from the System/360 Model 67" (i.e., it was now generally available)

- It included "multiprocessor configurations, with a high degree of system availability", with up to four processing units [while configurations with up to four processors were announced, only one and two processors configurations were actually built][1]

- It had "its own powerful operating system...[the] Time Sharing System monitor (TSS)" offering "virtually instantaneous access to and response from the computer" to "take advantage of the unique capabilities of a multiprocessor system"

- It offered "dynamic relocation of problem programs using the dynamic address translation facilities of the 2067 Processing Unit, permitting response, within seconds, to many simultaneous users"

Virtual memory

The S/360-67 design included a radical new component for implementing virtual memory, the "DAT box" (Dynamic Address Translation box). DAT on the 360/67 was based on the architecture outlined in a 1966 JACM paper by Arden, Galler, Westervelt, and O'Brien[4] and included both segment and page tables. The Model 67's virtual memory support was very similar to the virtual memory support that eventually became standard on the entire System/370 line.

The S/360-67 provided a 24- or 32-bit address space[1] – unlike the strictly 24-bit address space of other S/360 and early S/370 systems, and the 31-bit address space of S/370-XA available on later S/370s. The S/360-67 virtual address space was divided into pages (of 4096 bytes)[1] grouped into segments (of 1 million bytes); pages were dynamically mapped onto the processor's real memory. These S/360-67 features plus reference and change bits as part of the storage key enabled operating systems to implement demand paging: referencing a page that was not in memory caused a page fault, which in turn could be intercepted and processed by an operating system interrupt handler.

The S/360-67's virtual memory system was capable of meeting three distinct goals:

- Large address space. It mapped physical memory onto a larger pool of virtual memory, which could be dynamically swapped in and out of real memory as needed from random-access storage (typically: disk or drum storage).

- Isolated OS components. It made it possible to remove most of the operating system's memory footprint from the user's environment, thereby increasing the memory available for application use, and reducing the risk of applications intruding into or corrupting operating system data and programs.

- Multiple address spaces. By implementing multiple virtual address spaces, each for a different user, each user could potentially have a private virtual machine.

The first goal removed (for decades, at least) a crushing limitation of earlier machines: running out of physical storage. The second enabled substantial improvements in security and reliability. The third enabled the implementation of true virtual machines. Contemporary documents make it clear that full hardware virtualization and virtual machines were not original design goals for the S/360-67.

Features

The S/360-67 included the following extensions in addition to the standard and optional features available on all S/360 systems:[1]

- Dynamic Address Translation (DAT) with support for 24 or 32-bit virtual addresses using segment and page tables (up to 16 segments each containing up to 256 4096 byte pages)

- Extended PSW Mode that enables additional interrupt masking and additional control registers

- High Resolution Interval Timer with a resolution of approximately 13 microseconds

- Reference and change bits as part of storage protection keys

- Extended Direct Control allowing the processors in a duplex configuration to present an external interrupt to the other processor

- Partitioning of the processors, processor storage, and I/O channels in a duplex configuration into two separate subsystems

- Floating Addressing to allow processor storage in a partitioned duplex configuration to be assigned consecutive real memory addresses

- A Channel Controller that allows both processors in a duplex configuration to access all of the I/O channels and that allows I/O interrupts to be presented to either processor independent of what processor initiated the I/O operation

- Simplex configurations can include 7 I/O channels, while duplex configurations can include 14 I/O channels

- Three new supervisor-state instructions: Load Multiple Control (LMC), Store Multiple Control (SMC), Load Real Address (LRA)

- Two new problem-state instructions: Branch and Store Register (BASR), and Branch and Store (BAS)

- Two new program interruptions: Segment translation exception (16) and page translation exception (17)

The S/360-67 operated with a basic internal cycle time of 200 nanoseconds and a basic 750 nanosecond magnetic core storage cycle, the same as the S/360-65.[1] The 200 ns cycle time put the S/360-67 in the middle of the S/360 line, between the Model 30 at the low end and the Model 195 at the high end. From 1 to 8 bytes (8 data bits and 1 parity bit per byte) could be read or written to processor storage in a single cycle. A 60-bit parallel adder facilitated handling of long fractions in floating-point operations. An 8-bit serial adder enabled simultaneous execution of floating point exponent arithmetic, and also handled decimal arithmetic and variable field length (VFL) instructions.

New components

Four new components were part of the S/360-67:

- 2067 Processing Unit Models 1 and 2,

- 2365 Processor Storage Model 12,

- 2846 Channel Controller, and

- 2167 Configuration Unit.

These components, together with the 2365 Processor Storage Model 2, 2860 Selector Channel, 2870 Multiplexer Channel, and other System/360 control units and devices were available for use with the S/360-67.

Note that while Carnegie Tech had a 360/67 with an IBM 2361 LCS, that option was not listed in the price book and may not have worked in a duplex configuration.

Basic Configurations

Three basic configurations were available for the IBM System/360 model 67:

- Simplex—one IBM 2067-1 processor, two to four IBM 2365-2 Processor Storage components (512K to 1M bytes), up to seven data channels, and other peripherals. This system was called the IBM System/360 model 67-1.

- Half-duplex—one IBM 2067-2 processor, two to four IBM 2365-12 Processor Storage components (512K to 1M bytes), one IBM 2167 Configuration Unit, one or two IBM 2846 Channel Controllers, up to fourteen data channels, and other peripherals.

- Duplex—two IBM 2067-2 processors, three to eight IBM 2365-12 Processor Storage components (768K to 2M bytes), one IBM 2167 Configuration Unit, one or two IBM 2846 Channel Controllers, up to fourteen data channels, and other peripherals.

A half-duplex system could be upgraded in the field to a duplex system by adding one IBM 2067-2 processor and the third IBM 2365-12 Processor Storage, unless the half-duplex system already had three or more. The half-duplex and duplex configurations were called the IBM System/360 model 67-2.

Operating systems

When the S/360-67 was announced in August 1965, IBM also announced TSS/360, a time-sharing operating system project that was canceled in 1971 (having also been canceled in 1968, but reprieved in 1969).

IBM's failure to deliver TSS/360 as promised opened the door for others to develop operating systems that would use the unique features of the S/360-67:

- MTS, the Michigan Terminal System, was the time-sharing operating system developed at the University of Michigan and first used on the Model 67 in January 1967. Virtual memory support was added to MTS in October 1967. Multi-processor support for a duplex S/360-67 was added in October 1968.[8]

- CP/CMS was the first virtual machine operating system. Developed at IBM's Cambridge Scientific Center (CSC) near MIT. CP/CMS was essentially an unsupported research system, built away from IBM's mainstream product organizations, with active involvement of outside researchers. Over time it evolved into a fully supported IBM operating system (VM/370 and today's z/VM).

- VP/CSS was developed by National CSS to provide commercial time-sharing services. It was based upon CP/CMS.

Legacy

The S/360-67 had an important legacy. After the failure of TSS/360, IBM was surprised by the blossoming of a time-sharing community on the S/360-67 platform (CP/CMS, MTS, MUSIC). A large number of commercial, academic, and service bureau sites installed the system. By taking advantage of IBM's lukewarm support for time-sharing, and by sharing information and resources (including source code modifications), they built and supported a generation of time-sharing centers.

The unique features of the S/360-67 were initially not carried into IBM's next product series, the System/370, although the 370/145 had an associative memory that appeared more useful for paging than for its ostensible purpose.[9] This was largely fallout from a bitter and highly visible political battle within IBM over the merits of time-sharing versus batch processing. Initially at least, time-sharing lost.

However, IBM faced increasing customer demand for time-sharing and virtual memory capabilities. IBM also could not ignore the large number of S/360-67 time-sharing installations – including the new industry of time-sharing vendors, such as National CSS[10][11] and Interactive Data Corporation (IDC),[12] that were quickly achieving commercial success.

In 1972, IBM added virtual memory features to the entire S/370 series, a move seen by many as a vindication of work done on the S/360-67 project. The survival and success of IBM's VM family, and of virtualization technology in general, also owe much to the S/360-67.

In 2010, in the technical description of its latest mainframe, the z196, IBM stated that its software virtualization started with the System/360 model 67.[13]

References

- E.W. Pugh, L.R. Johnson, and John H. Palmer, IBM's 360 and early 370 systems, MIT Press, Cambridge MA and London, ISBN 0-262-16123-0, includes extensive (819 pp.) treatment of IBM's offerings during this period

- Melinda Varian, VM and the VM community, past present, and future, SHARE 89 Sessions 9059-9061, 1997

- 1 2 3 4 5 6 IBM System/360 Model 67 Functional Characteristics, Third Edition (February 1972), IBM publication GA27-2719-2

- ↑ The IBM 360/67 and CP/CMS, Tom Van Vleck, 1995, 1997, 2005, 2009

- 1 2 "A History of MTS—30 Years of Computing Service", Susan Topol, Information Technology Digest, Volume 5, No. 5 (May 13, 1996), University of Michigan

- 1 2 "Program and Addressing Structure in a Time-Sharing Environment", B. W. Arden , B. A. Galler , T. C. O'Brien , F. H. Westervelt, Journal of the ACM (JACM), v.13 n.1, p.1-16, Jan. 1966

- ↑ "System/360 Dates and characteristics" at IBM Archives > Exhibits > IBM Mainframes > Mainframes reference room > Mainframes basic information sources

- ↑ DIGITAL COMPUTER NEWSLETTER, Office of Naval Research, Mathematical Sciences Division, July 1965--pages 5-6: IBM System/360 time-sharing computers

- ↑ Varian, op. cit., p. 17 (Note 54) – S/360-67 announcement

- ↑ Pugh, op. cit., p. 364 – MTS on dual processor S/360-67 in 1968

- ↑ IBM. IBM Maintenance Library 3145 Processing Unit Theory - Maintenance. SY24-3581-2.:CPU 117–129

- ↑ "A technical history of National CSS", Harold Feinleib, Computer History Museum (March 2005)

- ↑ "From the very beginning… from my vantage point ― early history of National CSS", Dick Orenstein, Computer History Museum (January 2005)

- ↑ Varian, op. cit., pp. 24, Note 76 – IDC systems (quoting Dick Bayles)

- ↑ SG24-7832-00: IBM zEnterprise System Technical Introduction, page 57: “Starting in 1967, IBM has continuously provided software virtualization in its mainframe servers.”

External links

- A. Padegs, "System/360 and Beyond", IBM Journal of Research & Development, vol. 25 no. 5, pp. 377-390, September 1981

- IBM System/360 System Summary, thirteenth edition, January 1974, IBM publication GA22-6810-12, pages 6–13 to 6-15 describe the model 67

- IBM System/360 Model 67 Reference Data (Blue card)

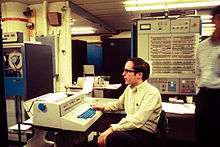

- Several photos of a dual processor IBM 360/67 at the University of Michigan's academic Computing Center in the late 1960s or early 1970s are included in Dave Mills' article describing the Michigan Terminal System (MTS)

- Pictures of an IBM S/360-67 at Newcastle (UK) University

- TSS/360 Concepts and Facilities

- Time-sharing in the IBM System/360 model 67