555 timer IC

|

NE555 from Signetics in dual-in-line package | |

| Type | Active, Integrated circuit |

|---|---|

| Invented | Hans Camenzind |

| First production | 1971 |

| Pin configuration | GND, TRIG, OUT, RESET, CTRL, THR, DIS, VCC |

| Electronic symbol | |

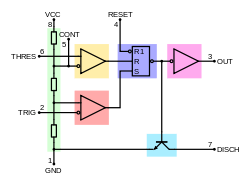

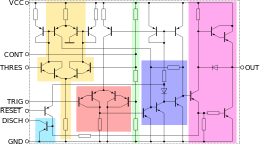

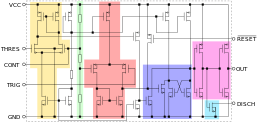

Internal block diagram | |

The 555 timer IC is an integrated circuit (chip) used in a variety of timer, pulse generation, and oscillator applications. The 555 can be used to provide time delays, as an oscillator, and as a flip-flop element. Derivatives provide up to four timing circuits in one package.

Introduced in 1971 by American company Signetics, the 555 is still in widespread use due to its low price, ease of use, and stability. It is now made by many companies in the original bipolar and also in low-power CMOS types. As of 2003, it was estimated that 1 billion units are manufactured every year.[1]

Design

The IC was designed in 1971 by Hans R. Camenzind under contract to Signetics, which was later acquired by Dutch company Philips Semiconductors (now NXP).

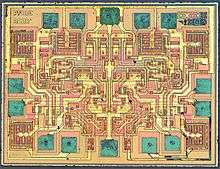

Depending on the manufacturer, the standard 555 package includes 25 transistors, 2 diodes and 15 resistors on a silicon chip installed in an 8-pin mini dual-in-line package (DIP-8).[2] Variants available include the 556 (a 14-pin DIP combining two 555s on one chip), and the two 558 & 559s (both a 16-pin DIP combining four slightly modified 555s with DIS & THR connected internally, and TR is falling edge sensitive instead of level sensitive).

The NE555 parts were commercial temperature range, 0 °C to +70 °C, and the SE555 part number designated the military temperature range, −55 °C to +125 °C. These were available in both high-reliability metal can (T package) and inexpensive epoxy plastic (V package) packages. Thus the full part numbers were NE555V, NE555T, SE555V, and SE555T. It has been hypothesized that the 555 got its name from the three 5 kΩ resistors used within,[3] but Hans Camenzind has stated that the number was arbitrary.[1]

Low-power versions of the 555 are also available, such as the 7555 and CMOS TLC555.[4] The 7555 is designed to cause less supply noise than the classic 555 and the manufacturer claims that it usually does not require a "control" capacitor and in many cases does not require a decoupling capacitor on the power supply. Those parts should generally be included, however, because noise produced by the timer or variation in power supply voltage might interfere with other parts of a circuit or influence its threshold voltages.

Pins

The connection of the pins for a DIP package is as follows:

| Pin | Name | Purpose |

|---|---|---|

| 1 | GND | Ground reference voltage, low level (0 V) |

| 2 | TRIG | The OUT pin goes high and a timing interval starts when this input falls below 1/2 of CTRL voltage (which is typically 1/3 VCC, CTRL being 2/3 VCC by default if CTRL is left open). |

| 3 | OUT | This output is driven to approximately 1.7 V below +VCC, or to GND. |

| 4 | RESET | A timing interval may be reset by driving this input to GND, but the timing does not begin again until RESET rises above approximately 0.7 volts. Overrides TRIG which overrides THR. |

| 5 | CTRL | Provides "control" access to the internal voltage divider (by default, 2/3 VCC). |

| 6 | THR | The timing (OUT high) interval ends when the voltage at THR ("threshold") is greater than that at CTRL (2/3 VCC if CTRL is open). |

| 7 | DIS | Open collector output which may discharge a capacitor between intervals. In phase with output. |

| 8 | VCC | Positive supply voltage, which is usually between 3 and 15 V depending on the variation. |

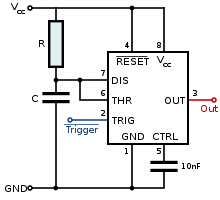

Pin 5 is also sometimes called the CONTROL VOLTAGE pin. By applying a voltage to the CONTROL VOLTAGE input one can alter the timing characteristics of the device. In most applications, the CONTROL VOLTAGE input is not used. It is usual to connect a 10 nF capacitor between pin 5 and 0 V to prevent interference. The CONTROL VOLTAGE input can be used to build an astable multivibrator with a frequency-modulated output.

Modes

The IC 555 has three operating modes:

- Bistable mode or Schmitt trigger – the 555 can operate as a flip-flop, if the DIS pin is not connected and no capacitor is used. Uses include bounce-free latched switches.

- Monostable mode – in this mode, the 555 functions as a "one-shot" pulse generator. Applications include timers, missing pulse detection, bouncefree switches, touch switches, frequency divider, capacitance measurement, pulse-width modulation (PWM) and so on.

- Astable (free-running) mode – the 555 can operate as an electronic oscillator. Uses include LED and lamp flashers, pulse generation, logic clocks, tone generation, security alarms, pulse position modulation and so on. The 555 can be used as a simple ADC, converting an analog value to a pulse length (e.g., selecting a thermistor as timing resistor allows the use of the 555 in a temperature sensor and the period of the output pulse is determined by the temperature). The use of a microprocessor-based circuit can then convert the pulse period to temperature, linearize it and even provide calibration means.

Bistable

In bistable (also called Schmitt trigger) mode, the 555 timer acts as a basic flip-flop. The trigger and reset inputs (pins 2 and 4 respectively on a 555) are held high via pull-up resistors while the threshold input (pin 6) is simply floating. Thus configured, pulling the trigger momentarily to ground acts as a 'set' and transitions the output pin (pin 3) to Vcc (high state). Pulling the reset input to ground acts as a 'reset' and transitions the output pin to ground (low state). No timing capacitors are required in a bistable configuration. Pin 5 (control voltage) is connected to ground via a small-value capacitor (usually 0.01 to 0.1 μF). Pin 7 (discharge) is left floating.[5]

Monostable

.png)

The output pulse ends when the voltage on the capacitor equals 2/3 of the supply voltage. The output pulse width can be lengthened or shortened to the need of the specific application by adjusting the values of R and C.[6]

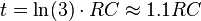

The output pulse width of time t, which is the time it takes to charge C to 2/3 of the supply voltage, is given by

where t is in seconds, R is in ohms (resistance) and C is in farads (capacitance).

While using the timer IC in monostable mode, the main disadvantage is that the time span between any two triggering pulses must be greater than the RC time constant.[7] Conversely, ignoring closely spaced pulses is done by setting the RC time constant to be larger than the span between spurious triggers. (Example: ignoring switch contact bouncing.)

Astable

In astable mode, the 555 timer puts out a continuous stream of rectangular pulses having a specified frequency. Resistor R1 is connected between VCC and the discharge pin (pin 7) and another resistor (R2) is connected between the discharge pin (pin 7), and the trigger (pin 2) and threshold (pin 6) pins that share a common node. Hence the capacitor is charged through R1 and R2, and discharged only through R2, since pin 7 has low impedance to ground during output low intervals of the cycle, therefore discharging the capacitor.

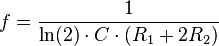

In the astable mode, the frequency of the pulse stream depends on the values of R1, R2 and C:

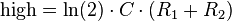

The high time from each pulse is given by:

and the low time from each pulse is given by:

where R1 and R2 are the values of the resistors in ohms and C is the value of the capacitor in farads.

The power capability of R1 must be greater than  .

.

Particularly with bipolar 555s, low values of  must be avoided so that the output stays saturated near zero volts during discharge, as assumed by the above equation. Otherwise the output low time will be greater than calculated above. The first cycle will take appreciably longer than the calculated time, as the capacitor must charge from 0V to 2/3 of VCC from power-up, but only from 1/3 of VCC to 2/3 of VCC on subsequent cycles.

must be avoided so that the output stays saturated near zero volts during discharge, as assumed by the above equation. Otherwise the output low time will be greater than calculated above. The first cycle will take appreciably longer than the calculated time, as the capacitor must charge from 0V to 2/3 of VCC from power-up, but only from 1/3 of VCC to 2/3 of VCC on subsequent cycles.

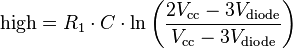

To have an output high time shorter than the low time (i.e., a duty cycle less than 50%) a small diode (that is fast enough for the application) can be placed in parallel with R2, with the cathode on the capacitor side. This bypasses R2 during the high part of the cycle so that the high interval depends only on R1 and C, with an adjustment based the voltage drop across the diode. The voltage drop across the diode slows charging on the capacitor so that the high time is a longer than the expected and often-cited ln(2)*R1C = 0.693 R1C. The low time will be the same as above, 0.693 R1C. With the bypass diode, the high time is

where Vdiode is when the diode's "on" current is 1/2 of Vcc/R1 which can be determined from its datasheet or by testing. As an extreme example, when Vcc= 5 and Vdiode= 0.7, high time = 1.00 R1C which is 45% longer than the "expected" 0.693 R1C. At the other extreme, when Vcc= 15 and Vdiode= 0.3, the high time = 0.725 R1C which is closer to the expected 0.693 R1C. The equation reduces to the expected 0.693 R1C if Vdiode= 0.

The operation of RESET in this mode is not well-defined. Some manufacturers' parts will hold the output state to what it was when RESET is taken low, others will send the output either high or low.

The astable configuration, with two resistors, cannot produce a 50% duty cycle. To produce a 50% duty cycle, eliminate R1, disconnect pin 7 and connect the supply end of R2 to pin 3, the output pin. This circuit is similar to using an inverter gate as an oscillator, but with fewer components than the astable configuration, and a much higher power output than a TTL or CMOS gate. The duty cycle for either the 555 or inverter-gate timer will not be precisely 50% due to the fact the timing network is supplied from the devices output pin, which has different internal resistances depending on whether it is in the high or low state (high side drivers tend to be more resistive).

Specifications

These specifications apply to the NE555. Other 555 timers can have different specifications depending on the grade (military, medical, etc.).

| Supply voltage (VCC) | 4.5 to 15 V |

| Supply current (VCC = +5 V) | 3 to 6 mA |

| Supply current (VCC = +15 V) | 10 to 15 mA |

| Output current (maximum) | 200 mA |

| Maximum Power dissipation | 600 mW |

| Power consumption (minimum operating) | 30 mW@5V, 225 mW@15V |

| Operating temperature | 0 to 70 °C |

Derivatives

Many pin-compatible variants, including CMOS versions, have been built by various companies. Bigger packages also exist with two or four timers on the same chip. The 555 is also known under the following type numbers:

| Manufacturer | Model | Remark |

|---|---|---|

| Custom Silicon Solutions[9] | CSS555/CSS555C | CMOS from 1.2 V, IDD < 5 µA |

| CEMI | ULY7855 | |

| ECG Philips | ECG955M | |

| Exar | XR-555 | |

| Fairchild Semiconductor | NE555/KA555 | |

| GoldStar | GSC555 | CMOS |

| Harris | HA555 | |

| Hitachi | HA17555 | |

| IK Semicon | ILC555 | CMOS from 2 V |

| Intersil | SE555/NE555 | |

| Intersil | ICM7555 | CMOS |

| Lithic Systems | LC555 | |

| Maxim | ICM7555 | CMOS from 2 V |

| Motorola | MC1455/MC1555 | |

| National Semiconductor | LM1455/LM555/LM555C | |

| National Semiconductor | LMC555 | CMOS from 1.5 V |

| NTE Sylvania | NTE955M | |

| Raytheon | RM555/RC555 | |

| RCA | CA555/CA555C | |

| STMicroelectronics | NE555N/ K3T647 | |

| STMicroelectronics | TS555 | CMOS from 2 V |

| Texas Instruments | SN52555/SN72555 | |

| Texas Instruments | TLC555 | CMOS from 2 V |

| USSR | К1006ВИ1 | |

| X-REL Semiconductor | XTR655 | Operation from -60°C to 250+°C |

| Zetex | ZSCT1555 (discontinued) | down to 0.9 V |

| NXP Semiconductors | ICM7555 | CMOS |

| HFO / East Germany | B555 |

556 dual timer

The dual version is called 556. It features two complete 555s in a 14 pin DIL package.

558 quad timer

The quad version is called 558 and has 16 pins. To fit four 555s into a 16 pin package the power, control voltage, and reset lines are shared by all four modules. Each module's discharge and threshold circuits are wired together internally.

Example applications

Joystick interface circuit using the 558 quad timer

The Apple II microcomputer used a quad timer 558 in monostable (or "one-shot") mode to interface up to four "game paddles" or two joysticks to the host computer. It also used a single 555 for flashing the display cursor.

A similar circuit was used in the IBM PC.[10] In the joystick interface circuit of the IBM PC, the capacitor of the RC network (see Monostable Mode above) was generally a 10 nF capacitor. The resistor of the RC network consisted of the potentiometer inside the joystick along with an external resistor of 2.2 kΩ.[11] The joystick potentiometer acted as a variable resistor. By moving the joystick, the resistance of the joystick increased from a small value up to about 100 kΩ. The joystick operated at 5 V.[12]

Software running in the host computer started the process of determining the joystick position by writing to a special address (ISA bus I/O address 201h).[12][13] This would result in a trigger signal to the quad timer, which would cause the capacitor of the RC network to begin charging and cause the quad timer to output a pulse. The width of the pulse was determined by how long it took the C to charge up to 2/3 of 5 V (or about 3.33 V), which was in turn determined by the joystick position.[12][14] The software then measured the pulse width to determine the joystick position. A wide pulse represented the full-right joystick position, for example, while a narrow pulse represented the full-left joystick position.[12]

See also

- Counter (digital)

- Operational amplifier

- List of LM-series integrated circuits

- 4000 series, List of 4000 series integrated circuits

- 7400 series, List of 7400 series integrated circuits

References

- 1 2 Ward, Jack (2004). The 555 Timer IC – An Interview with Hans Camenzind. The Semiconductor Museum. Retrieved 2010-04-05

- ↑ van Roon, Fig 3 & related text.

- ↑ Scherz, Paul (2000) "Practical Electronics for Inventors", p. 589. McGraw-Hill/TAB Electronics. ISBN 978-0-07-058078-7. Retrieved 2010-04-05.

- ↑ Jung, Walter G. (1983) "IC Timer Cookbook, Second Edition", pp. 40–41. Sams Technical Publishing; 2nd ed. ISBN 978-0-672-21932-0. Retrieved 2010-04-05.

- ↑ 555-timer-circuits.com

- ↑ van Roon, Chapter "Monostable Mode". (Using the 555 timer as a logic clock)

- ↑ national.com

- ↑ van Roon Chapter: "Astable operation".

- ↑ customsiliconsolutions.co

- ↑ Engdahl, pg 1.

- ↑ Engdahl, "Circuit diagram of PC joysyck interface"

- 1 2 3 4 epanorama.net

- ↑ Eggebrecht, p. 197.

- ↑ Eggebrecht, pp. 197-99

Further reading

- 555 Timer Applications Sourcebook Experiments; H. Berlin; BPB Publications; 218 pages; 2008; ISBN 978-8176567909.

- Timer, Op Amp, and Optoelectronic Circuits and Projects; Forrest Mims III; Master Publishing; 128 pages; 2004; ISBN 978-0-945053-29-3.

- Engineer's Mini-Notebook – 555 Timer IC Circuits; Forrest Mims III; Radio Shack; 33 pages; 1989; ASIN B000MN54A6.

- IC Timer Cookbook; 2nd Ed; Walter G Jung; Sams Publishing; 384 pages; 1983; ISBN 978-0-672-21932-0.

- 555 Timer Applications Sourcebook with Experiments; Howard M Berlin; Sams Publishing; 158 pages; 1979; ISBN 978-0-672-21538-4.

- IC 555 Projects; E.A. Parr; Bernard Babani Publishing; 144 pages; 1978; ISBN 978-0-85934-047-2.

- Analog Applications Manual; Signetics; 418 pages; 1979. Chapter 6 Timers is 22 pages.

External links

| Wikimedia Commons has media related to 555 timer IC. |

- 555 Timer Circuits – the Astable, Monostable and Bistable

- Simple 555 timer circuits

- Java simulation of 555 oscillator circuit

- NE555 Frequency and duty cycle calculator for astable multivibrators

- Using NE555 as a Temperature DSP

- 555 Timer Tutorial by Tony van Roon

- Common Mistakes When Using a 555 Timer

- 555 and 556 Timer Circuits

- 555 using areas and examples circuits

- Working with 555 Timer Circuits Engineers Garage

- Analysis and synthesis of a 555 astable multivibrator circuit - online calculator

- Online simulations of a 555 astable multivibrator circuit - online simulator

- IC Datasheets

- NE555, Single Bipolar Timer, Texas Instruments

- NE556, Dual Bipolar Timer, Texas Instruments

- NE558, Quad Bipolar Timer, NXP

- LMC555, Single CMOS Timer, Texas Instruments (operates down to 1.5 Volt at 50 uAmp)

- ICM755x, Single / Dual CMOS Timer, Intersil (operates down to 2.0 Volt at 60 uAmp)

- ZSCT1555, Single CMOS Timer, Diodes Inc (operates down to 0.9 Volt at 74 uAmp)

- TS300x, Single CMOS Timers, Touchstone (operates down to 0.9 Volt at 1.0 uAmp)

- XTR65x, HiRel HiTemp Timer, X-REL (operates from -60°C to 230°C)

| ||||||||||||||

|