UNIVAC 1100/2200 series

The UNIVAC 1100/2200 series is a series of compatible 36-bit computer systems, beginning with the UNIVAC 1107 in 1962, initially made by Sperry Rand. The series continues to be supported today by Unisys Corporation as the ClearPath Dorado Series. The solid-state 1107 model number was in the same sequence as the earlier vacuum-tube computers, but the early computers were not compatible with the solid-state successors.

Architecture

Data formats

- Fixed-point, either integer or fraction

- Whole word – 36-bit (ones' complement)

- Half word – two 18-bit fields per word (unsigned or ones' complement)

- Third word – three 12-bit fields per word (ones' complement)

- Quarter word – four nine-bit fields per word (unsigned)

- Sixth word – six six-bit fields per word (unsigned)

- Floating point

- Single precision – 36 bits: one sign bit, eight-bit characteristic, 27-bit mantissa

- Double precision – 72 bits: one sign bit, 11-bit characteristic, 60-bit mantissa

- Alphanumeric

Instruction Format

Instructions are 36 bits long with the following fields:

- f (6 bits) - function designator (opcode),

- j (4 bits) - partial word designator, J-register designator, or minor function designator,

- a (4 bits) - register (A, X, or R) designator or I/O designator,

- x (4 bits) - index register (X) designator,

- h (1 bit ) - index register increment designator,

- i (1 bit) - indirect address designator,

- u (16 bits) - address or operand designator.

| Address | Register | Contents | |

|---|---|---|---|

| 000 | Unused | Unused | |

| 001 | X1 | Increment | Modifier |

| ... | ... | Increment | Modifier |

| 013 | X11 | Increment | Modifier |

| 014 | X12/A0 | Overlap (X or A) | |

| ... | ... | Overlap (X or A) | |

| 017 | X15/A3 | Overlap (X or A) | |

| 020 | A4 | Accumulator | |

| ... | ... | Accumulator | |

| 033 | A15 | Accumulator | |

| 034 | A15+1 | Unassigned (A) | |

| ... | ... | Unassigned (A) | |

| 037 | A15+4 | Unassigned (A) | |

| ... | Executive | Protected Executive | |

| 101 | R1 | Special (R) | |

| ... | ... | Special (R) | |

| 117 | R15 | Special (R) | |

| ... | Executive | Protected Executive | |

| 177 | Executive | Protected Executive | |

Registers

The 128 registers of the high speed "general register stack" ("integrated circuit registers" on the UNIVAC 1108 and UNIVAC 1106 models), map to the current data space in main storage starting at memory address zero. These registers include both user and executive copies of the A, X, R, and J registers and many special function executive registers.

The table on the right shows the addresses (in octal) of the user registers.

There are 15 index registers (X1 ... X15), 16 accumulators (A0 ... A15), and 15 special function user registers (R1 .. R15). The 4 J registers and 3 "staging registers" are uses of some of the special function R registers.

One interesting feature is that the last four index registers (X12 ... X15) and the first four accumulators (A0 ... A3) overlap, allowing data to be interpreted either way in these registers. This also results in four unassigned accumulators (A15+1 ... A15+4) that can only be accessed by their memory address (double word instructions on A15 do operate on A15+1).

Vacuum tube machines not mutually compatible

These machines had different architectures and word sizes and were not compatible with each other. They all used vacuum tubes and many used drum memory as their main memory. Some were designed by Engineering Research Associates (ERA) which was later purchased and merged with the UNIVAC company.

The UNIVAC 1101, or ERA 1101, was a computer system designed by ERA and built by the Remington Rand corporation in the 1950s. It was never sold commercially. [1] The UNIVAC 1102 or ERA 1102 was designed by Engineering Research Associates for the United States Air Force. The 36-bit UNIVAC 1103 was introduced in 1953 and an upgraded version (UNIVAC 1103A) was released in 1956. This was the first commercial computer to use core memory instead of the Williams tube. The UNIVAC 1105 was the successor to the 1103A, and was introduced in 1958.

The UNIVAC 1104 system was a 30-bit version of the 1103 built for Westinghouse Electric, in 1957, for use on the BOMARC Missile Program. However, by the time the BOMARC was deployed in the 1960s, a more modern computer (a version of the AN/USQ-20, designated the G-40) had replaced the UNIVAC 1104.

UNIVAC 1100 compatible series

These machines had a common architecture and word size. They all used transistorized electronics and integrated circuits. Early machines used core memory (the 1110 used plated wire memory) until that was replaced with semiconductor memory in 1975.

1107

The UNIVAC 1107 was the first solid-state member of Sperry Univac's UNIVAC 1100 series of computers, introduced in October 1962. It was also known as the Thin-Film Computer because of its use of thin-film memory for its register storage. It represented a marked change of architecture: unlike previous models, it was not a strict two-address machine: it was a single-address machine with up to 65,536 words of 36-bit core memory. The machine's registers were stored in 128 words of thin-film memory, a faster form of magnetic storage. With six cycles of thin-film memory per 4 microsecond main memory cycle, address indexing was performed without a cycle time penalty. Only 36 systems were sold.

The core memory was available in 16,384 36-bit words in a single bank; or in increments of 16,384 words to a maximum of 65,536 words in two separately accessed banks. With a cycle time of 4 microseconds, the effective cycle time was 2 microseconds when instruction and data accesses overlapped in two banks.

The 128-word thin-film memory general register stack (16 each arithmetic, index, and repeat with a few in common) had a 300-nanosecond access time with a complete cycle time of 600 nanoseconds. Six cycles of thin-film memory per core memory cycle and fast adder circuitry permitted memory address indexing within the current instruction core memory cycle and also modification of the index value (the signed upper 18 bits were added to the lower 18 bits) in the specified index register (16 were available). The 16 input/output (I/O) channels also used thin-film memory locations for direct to memory I/O memory location registers. Programs could not be executed from unused thin-film memory locations.

Both UNISERVO IIA and UNISERVO III tape drives were supported, both of which could use either metallic (UNIVAC I) or mylar tape.

The FH880 drum memory unit was also supported as a spooling and file-storage media. Spinning at 1800 RPM, it stored approximately 300,000 36-bit words.

Univac provided a batch operating system, EXEC I. Computer Sciences Corporation was contracted to provide a powerful optimizing Fortran IV compiler, an assembler named SLEUTH with sophisticated macro capabilities, and a very flexible linking loader.

1108

The 1108 was introduced in 1964. Integrated circuits replaced the thin film memory that the UNIVAC 1107 used for register storage. Smaller and faster cores, compared to the 1107, were used for main memory.

In addition to faster components, two significant design improvements were incorporated: base registers and additional hardware instructions. The two 18-bit base registers (one for instruction storage and one for data storage) permitted dynamic relocation: as a program got swapped in and out of main memory, its instructions and data could be placed anywhere each time it got reloaded. To support multiprogramming, the 1108 had memory protection using two base and limit registers, with 512-word resolution. One was called the I-bank or instruction bank, and the other the D-bank or data bank. If the I-bank and D-bank of a program were put into different physical banks of memory, a 1/2 microsecond advantage accrued, called "alternate bank timing."

The additional hardware instructions included double precision arithmetic, double-word load, store, and comparison instructions. The processor could have up to 16 input/output channels for peripherals.

Just as the first UNIVAC 1108 systems were being delivered in 1965, Sperry Rand announced the UNIVAC 1108 II (also known as the UNIVAC 1108A) which had support for multiprocessing: up to three CPUs, four memory banks totaling 262,144 words, and two independent programmable input/output controllers (IOCs). With everything busy, five activities could be going on at the same moment: three programs running in the CPUs and two input/output processes in the IOCs. One more instruction was incorporated: test-and-set, to provide for synchronization between the CPUs.

Although a 1964 internal study indicated only about 43 might sell, in all, 296 processors were produced.

When Sperry Rand replaced the core memory with semiconductor memory, the same machine was released as the UNIVAC 1100/20. In this new naming convention, the final digit represented the number of CPUs (e.g., 1100/22 was a system with two CPUs) in the system.

It was the first multiprocessor machine in the series, capable of expansion to three CPUs and two IOCs (Input/Output Control Units). To support this, it had up to 262,144 words of eight-ported main memory: separate instruction and data paths for each CPU, and one path for each IOC. The memory was organized in physical banks of 65,536 words, with separate odd and even ports in each bank. The instruction set was very similar to that of the 1107, but included some additional instructions, including the "Test and Set" instruction for multiprocessor synchronization. Some models of the 1108 implemented the ability to divide words into four nine-bit bytes, allowing use of ASCII characters.

1106

The UNIVAC 1106 was introduced in December 1969 and was absolutely identical to the UNIVAC 1108 in instruction set. Like the 1108, it was multiprocessor capable, and it was not supplied with any IOCs. Early versions of the UNIVAC 1106 were simply half speed UNIVAC 1108 systems. Later Sperry Univac used a different memory system which was inherently slower and cheaper than that of the UNIVAC 1108. Sperry Univac sold a total of 338 processors in 1106 systems.

When Sperry Rand replaced the core memory with semiconductor memory, the same machine was released as the UNIVAC 1100/10.

1110

The UNIVAC 1110 was the fourth member of the series, introduced in 1972.

The UNIVAC 1110 had enhanced multiprocessing support: sixteen-way memory access allowed up to six CAUs (Command Arithmetic Unit, the new name for CPU and so called because the CAU no longer had any I/O capability) and four IOAUs (Input Output Access Units, the name for separate units which performed the I/O channel programs). It also had 'extended memory' cabinets accessible in a 'daisy chain' arrangement to augment main storage. The larger configurations, 6x4+ were used by NASA. It also introduced an extension to the instruction set, of 'Byte Instructions'.

When Sperry Rand replaced the plated wire memory with semiconductor memory, the same machine was released as the UNIVAC 1100/40. In this new naming convention, the final digit represented the number of CPUs in the system. The 1110 had four base and limit registers, so a program could access four 64k banks. New instructions were added to allow a program to change the contents of the banks, rather than the banks being fixed when the program was prepared

Sperry Rand sold a total of 290 processors in 1110 systems.

Semiconductor memory series

In 1975, Sperry Univac introduced a new series of machines with semiconductor memory replacing core, with a new naming convention:

An upgraded 1106 was called the UNIVAC 1100/10. In this new naming convention, the final digit represented the number of CPUs or CAUs in the system, so that, for example, a two-processor 1100/10 system was designated an 1100/12. An upgraded 1108 was called the UNIVAC 1100/20. An upgraded 1110 was released as the UNIVAC 1100/40.

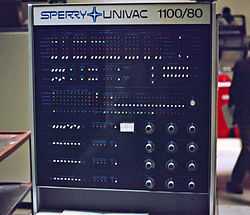

The UNIVAC 1100/60 was introduced in 1979. The UNIVAC 1100/70 was introduced in 1981. The UNIVAC 1100/80 was introduced in 1979. Intended to combine 1100 and 494 systems. The UNIVAC 1100/90 was introduced in 1982. It was liquid-cooled.

The 1100/80 introduced a cache memory - the SIU or Storage Interface Unit. It incorporated a mini-computer, based on the BC/7 (business computer) as a maintenance processor. This was used to load microcode, and for diagnostic purposes. Power was 400 Hz, to reduce large scale DC power supplies.

SPERRY 2200 series

In 1983 Sperry Corporation discontinued the name UNIVAC for their products.

- SPERRY 2200/100 introduced in 1985

- SPERRY Integrated Scientific Processor introduced in 1985

UNISYS 2200 series

In 1986 Sperry Corporation merges with Burroughs Corporation to become Unisys.

- UNISYS 2200/200 introduced in 1986

- UNISYS 2200/400 introduced in 1988

- UNISYS 2200/600 introduced in 1989

- UNISYS 2200/100 introduced in 1990

- UNISYS 2200/500 introduced in 1993

- UNISYS 2200/900 introduced in 1993

- UNISYS 2200/3800 introduced in 1997

UNISYS ClearPath IX series

In 1996 Unisys introduced the ClearPath IX series. The ClearPath machines are a common platform that implement either the 1100/2200 architecture (the ClearPath IX series) or the Burroughs large systems architecture (the ClearPath/MCP series). Everything is common except the actual CPUs, which are implemented as ASICs. In addition to the IX (1100/2200) CPUs and the MCP (Burroughs large systems) CPU, the architecture had Xeon (and briefly Itanium) CPUs. Unisys' goal was to provide an orderly transition for their 1100/2200 customers to a more modern architecture.

See also

- List of UNIVAC products

- Unisys OS 2200 operating system

- Unisys 2200 Series system architecture

- IBM 7090 IBM's top-of-the-line 36-bit computer series of the late 1950s.

References

- ↑ See Engineering Research Associates and the Atlas Computer (UNIVAC 1101) at wiki.cc.gatetech.edu

External links

- UNIVAC Memories

- A history of Univac computers and Operating Systems (PDF file)

- UNIVAC timeline

- The UNIVAC 1108

- UNIVAC 1108-II The big system with the big reputation (PDF)

- The Case 1107

- UNIVAC Thin-Film Memory Computer 1107

- Unisys History Newsletter. Volume 1, Number 3

- UNIVAC 1107 documentation on Bitsavers.org

| ||||||||||||||||||||||