TopoR

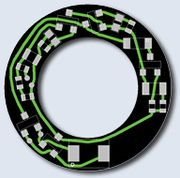

TopoR (Topological Router) is an EDA program developed and maintained by Eremex company, based in Russia. It is dedicated to laying out a printed circuit board (PCB). It currently lacks schematic capture and library editing (which have to be done using third-party software), but features a powerful autorouter and a set of tools intended to reduce the amount of effort needed for manual routing of a PCB. The most recognizable feature of TopoR is absence of preferred routing directions, which results in unusual looking PCBs.

History

Work on a flexible topological router began in 1988, when it became clear that the traditional methods of routing with regular and irregular grids (grid-based routers and shape-based routers) and consecutive wiring with locked-down geometry were a dead-end solution.

1996 saw the release of the first version of a topological router that actually came to be used by industrial enterprises. The FreeStyle Router ran under MS-DOS and successfully routed dual-layer boards. This early router showed the advantages of an innovative approach to routing and high efficiency of the models, algorithms, and software implementation. A 1.44MB floppy disk was enough for the program and accompanying examples; the routing was much faster and better than competitive products.

The first Windows version of the topological router was released in 2001 and named TopoR. The program routed not only dual-layer but also multilayer printed circuit boards.

General information

Compared to other CAD systems, TopoR dramatically reduces the total wire length and number of vias. TopoR successfully routes both single-layer and high-density multilayer boards.

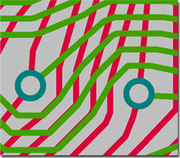

Routing of the wiring topology is done automatically and flexibly; angles are not limited to 90° and 45°.

Efficient use of PCB space and absence of preferred routing directions in layers considerably reduces electromagnetic crosstalks.

TopoR routes all connections, even if this entails violating design constraints. Such violations can be automatically corrected later. On densely packed boards this feature is crucial, because it helps assess both the possibility and workload for manual adjustments.

When you move objects (such as components and vias) around, wire length and shape are optimized automatically with appropriate clearance. This considerably simplifies the process of editing without making you care about observing design constraints.

The user is free to choose from two ways to calculate the wire shape: with or without arcs. The first method involves wires consisting of lines only. The other makes wires keep appropriate clearance when circling pads and consist of arcs and lines.

TopoR simultaneously optimizes several alternative variants of the layout. Variants with the worst parameters (total wire length and number of vias) will be removed. This approach allows the distributed routing mechanism to be used, which improves the speed of routing. According to the authors of TopoR, distributed routing will be available in a future release.

TopoR has an automatic component placement feature. The procedure can be used both for all components of the board and only for components in a specific area. It is not comparable to the quality of the manual placement, but it can be used as a preparation step for manual placement.

The minimum and desired clearances for each net can be specified.

TopoR automatically reduces the width of a wire that approaches a narrow pad (or one with a diameter that is less than the width of the wire), or when it passes through bottlenecks (for example, between the pads of a component).

Wire-to-pad transitions use teardrop-style smoothing. The use of this procedure at the design stage helps avoid violations in design-rule checking when teardrops are added in the CAM editor.

TopoR can recognize BGA (Ball Grid Array) component areas and apply a special strategy for routing them. This helps reduce the number of vias, the density of connections, and in some cases the number of routing layers.

TopoR is very effective for routing single-layer printed circuit boards, because it guarantees (within a particular layout) the absolute minimum of vias. During routing, TopoR either finds a single-layer solution or an alternative with as few vias as possible.

See also

Publications

- Luzin S., Polubasov O. Advantages of Isotropic PCB Routing.// Printed Circuit Design&Fab #6. 2009 pp.38-40.

- Polubasov O. Routing Concepts of a Topological Router CAD System. // Onboard Technology. #5. 2011. – pp.11-15..

- A. Lysenko, S. Luzin, O. Polubasov Synchronizing Delays in Signal Transmission Lines.// OnBoard technology #9. 2011. pp.14-17.

- S. Luzin, G. Petrosjan, O. Polubasov Problems In Routing of PCB with BGA Components.//OnBoard technology #11. 2009. pp.12-15.

- S. Popov, Iu. Popov Speed and improve PCB routing // EDN Network — December 05, 2013

Publications in Russian

- CHIP NEWS:

- Electronics, #5, 2005

- Electronic components:

- Modern electronics journal: