Subthreshold slope

The subthreshold slope is a feature of a MOSFET's current–voltage characteristic.

In the subthreshold region the drain current behaviour – though being controlled by the gate terminal – is similar to the exponentially increasing current of a forward biased diode. Therefore a plot of logarithmic drain current versus gate voltage with drain, source, and bulk voltages fixed will exhibit approximately log linear behaviour in this MOSFET operating regime. Its slope is the subthreshold slope.

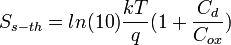

The subthreshold slope is closely related to its reciprocal value called subthreshold swing Ss-th which is usually given as:[1]

= depletion layer capacitance

= depletion layer capacitance

= gate-oxide capacitance

= gate-oxide capacitance

= thermal energy divided by the elementary charge

= thermal energy divided by the elementary charge

The minimum subthreshold swing of a conventional device can be found by letting  which yields 60 mV/dec at room temperature (300 K). A typical experimental subthreshold swing for a scaled MOSFET at room temperature is ~70 mV/dec, slightly degraded due to short-channel MOSFET parasitics.[2]

which yields 60 mV/dec at room temperature (300 K). A typical experimental subthreshold swing for a scaled MOSFET at room temperature is ~70 mV/dec, slightly degraded due to short-channel MOSFET parasitics.[2]

A dec (decade) corresponds to a 10 times increase of the drain current ID.

A device characterized by steep subthreshold slope exhibits a faster transition between off (low current) and on (high current) states.

References

- ↑ Physics of Semiconductor Devices, S. M. Sze. New York: Wiley, 3rd ed., with Kwok K. Ng, 2007, chapter 6.2.4, p. 315, ISBN 978-0-471-14323-9.

- ↑ Auth, C.; Allen, C.; Blattner, A.; Bergstrom, D.; Brazier, M.; Bost, M.; Buehler, M.; Chikarmane, V.; Ghani, T.; Glassman, T.; Grover, R.; Han, W.; Hanken, D.; Hattendorf, M.; Hentges, P.; Heussner, R.; Hicks, J.; Ingerly, D.; Jain, P.; Jaloviar, S.; James, R.; Jones, D.; Jopling, J.; Joshi, S.; Kenyon, C.; Liu, H.; McFadden, R.; McIntyre, B.; Neirynck, J.; Parker, C. (2012). "A 22nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors". 2012 Symposium on VLSI Technology (VLSIT). p. 131. doi:10.1109/VLSIT.2012.6242496. ISBN 978-1-4673-0847-2.

External links

- Optimization of Ultra-Low-Power CMOS Transistors; Michael Stockinger, 2000