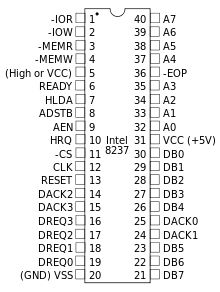

Intel 8237

Intel 8237 is a direct memory access (DMA) controller, a part of the MCS 85 microprocessor family. It enables data transfer between memory and the I/O with reduced load on the system's main processor by providing the memory with control signals and memory address information during the DMA transfer.

The 8237 is a four-channel device that can be expanded to include any number of DMA channel inputs. The 8237 is capable of DMA transfers at rates of up to 1.6 MByte per second. Each channel is capable of addressing a full 64k-byte section of memory and can transfer up to 64k bytes with a single programming.[1]

A single 8237 was used as the DMA controller in the original IBM PC and IBM XT. The IBM PC AT added another 8237 in master-slave configuration, increasing the number of DMA channels from four to seven.[2] Later IBM-compatible personal computers may have chip sets that emulate the functions of the 8237 for backward compatibility.

Modes

The 8237 operates in four different modes, depending upon the number of bytes transferred per cycle and number of ICs used:

- Single - One DMA cycle, one CPU cycle interleaved until address counter reaches zero.[3]

- Block - Transfer progresses until the word count reaches zero or the EOP signal goes active.[3]

- Demand - Transfers continue until TC or EOP goes active or DRQ goes inactive. The CPU is permitted to use the bus when no transfer is requested.[3]

- Cascade - Used to cascade additional DMA controllers. DREQ and DACK is matched with HRQ and HLDA from the next chip to establish a priority chain. Actual bus signals is executed by cascaded chip.[3]

Memory-to-memory transfer can be performed. This means data can be transferred from one memory device to another memory device. The channel 0 Current Address register is the source for the data transfer and channel 1 and the transfer terminates when Current Word Count register becomes 0. Channel 0 is used for DRAM refresh on IBM PC compatibles.[3]

In auto initialize mode the address and count values are restored upon reception of an end of process (EOP) signal. This happens without any CPU intervention. It is used to repeat the last transfer.[3]

The terminal count (TC) signals end of transfer to ISA cards. At the end of transfer an auto initialize will occur configured to do so.

Single mode

In single mode only one byte is transferred per request. For every transfer, the counting register is decremented and address is incremented or decremented depending on programming. When the counting register reaches zero, the terminal count TC signal is sent to the card.[4][5]

The DMA request DREQ must be raised by the card and held active until it is acknowledged by the DMA acknowledge DACK.[4]

Block transfer mode

The transfer is activated by DREQ which can be deactivated once acknowledged by DACK. The transfer continues until end of process EOP (either internal or external) is activated which will trigger terminal count TC to the card. Auto-initialization may be programmed in this mode.[4]

Demand transfer mode

The transfer is activated by DREQ and acknowledged by DACK and continues until either TC, external EOP or DREQ goes inactive. Only TC or external EOP may activate auto-initialization if this is programmed.[4]

Internal registers

The internal registers used in the 8237 for data transfer are as follows:

- Base address register: To store the initial address from where data transfer will take place

- Base word count register: To store the number of transfers to be performed

- Current address register: To store the current address from where data is being transferred

- Current word count register: To store the number of transfers remaining to be performed

- Temporary address register: To hold address of data during memory-to-memory transfer

- Temporary word count register: To hold number of transfers to be performed in memory-to-memory transfer

- Mode register: 8-bit register which stores the channel to be used, the operating mode, i.e. the transfer mode, and other transfer parameters

- Command register: 8-bit register which initializes the channel to be used for data transfer

- Request register: 8-bit register used to indicate which channel is requesting for data transfer

- Mask register: 8-bit register used to mask a particular channel from requesting for DMA service

- Status register: 8-bit register used to indicate which channel is currently under DMA service and some other parameters

IBM PC use

Although the 8237 was introduced with the 8-bit 8085 processor family, it is compatible with the 8086/88 microprocessors. A limitation on the IBM PC (AT) compatibles is that the 8237 at 0x00 and 74LS612 at 0x80 only can address 16 megabyte of memory; this is because the IBM AT, which introduced the dual 8237 DMA controller design, has an Intel 80286 microprocessor, which can directly address a maximum of 16 MB.[6] This means that for other memory areas the data has to be transferred to a buffer first, and then moved to the final memory by the CPU. This is called "bounce buffer".

Integration into chipsets

Although this device may not appear as a discrete component in modern personal computer systems, it does appear within system controller chip sets. For example, the 82875P ISP integrated system peripheral controller has two DMA internal controllers programmed almost exactly like the 8237.[7]

See also

- Intel 8284 - Clock generator

- Intel 8288 - Bus controller

- 8250 UART - Asynchronous serial controller (EIA-232)

- Intel 8253 - Programmable Interval Timer (PIT)

- Intel 8255 - Programmable Peripheral Interface (PPI)

- Intel 8259 - Programmable Interrupt Controller (PIC)

- Parallel ATA (P-ATA)

- Industry Standard Architecture (ISA)

- Input/output base address on IBM PC compatibles

References

- ↑ Intel microprocessors by Barry B Brey

- ↑ N. MATHIVANAN (2007). PC-BASED INSTRUMENTATION: CONCEPTS AND PRACTICE. PHI Learning Pvt. Ltd. pp. 227–229. ISBN 978-81-203-3076-4.

- ↑ 3.0 3.1 3.2 3.3 3.4 3.5 aluzina.org - Intel 8237/8237-2 High performance. Programmable DMA controller (.pdf) datasheet

- ↑ 4.0 4.1 4.2 4.3 books.google.com - Advanced Microprocessors And Peripherals, 2006 p312/313

- ↑ pinouts.ru - ISA bus pinout and wiring, 2008-10-20

- ↑ brokenthorn.com - Operating Systems Development Series

- ↑ http://www.datasheetarchive.com/pdf-datasheets/Databooks-2/Book261-1091.pdf

External links

- Introduction,pin configuration,block description

- DMA: What it is and How it Works FreeBSD Developers' Handbook. 1997 (internet archive).