Extreme ultraviolet lithography

.svg.png)

Extreme ultraviolet lithography (also known as EUV or EUVL) is a next-generation lithography technology using an extreme ultraviolet (EUV) wavelength, currently expected to be 13.5 nm. EUV is currently targeted for use at the 7 nm post-silicon node with customized off-axis illumination and multiple patterning. It was first targeted for 100 nm conventional patterning.[1] While source power is the chief concern due to its impact on productivity, significant changes in mask infrastructure, including blanks, pellicles and inspection, are also under study.

Light source

Neutral atoms or condensed matter cannot emit EUV radiation. Ionization must precede EUV emission in matter.Electrons must be bound to multicharged positive ions; for example, to remove an electron from a +3 charged carbon ion (three electrons already removed) requires about 65 eV.[2] Such electrons are more tightly bound than typical valence electrons. The thermal production of multicharged positive ions is only possible in a hot dense plasma, which itself strongly absorbs EUV.[3][4]

Xe or Sn plasma sources are either discharge-produced or laser-produced. Discharge-produced plasma is made by discharging a lightning bolt's worth of electric current through a tin vapor. Laser-produced plasma is made by microscopic droplets of molten tin heated by powerful laser. Laser-produced plasma sources (e.g., ASML's NXE:3300B scanner) outperform discharge-produced plasma sources. Power output exceeding 100 W is a requirement for sufficient throughput.

While state-of-the-art 193 nm ArF excimer lasers offer intensities of 200 W/cm2,[5] lasers for producing EUV-generating plasmas need to be much more intense, on the order of 1011 W/cm2.[6] This indicates the enormous energy burden imposed by switching from 193 nm light (power output approaching 100 W)[7] to EUV light (10 kW).[8] An EUV source driven by a 200 kW CO2 laser with ~10% wall plug efficiency[9] consumes an electrical power of ~2 MW, while a 100 W ArF immersion laser with ~1% wall plug efficiency[10] consumes an electrical power of ~10 kW. A state-of-the-art ArF immersion lithography 120 W light source requires no more than 40 kW[11] while EUV sources are targeted to exceed 40 kW.[12]

A further characteristic of the plasma-based EUV sources under development is that they are not even partially coherent,[13] unlike the KrF and ArF excimer lasers used for current optical lithography. Further power reduction (energy loss) is expected in converting incoherent sources (emitting in all possible directions at many independent wavelengths) to partially coherent (emitting in a limited range of directions within a narrow wavelength band) sources by filtering. Coherent light poses a risk of monochromatic reflection interference and mismatch of multilayer reflectance bandwidth.[14]

As of 2008, development tools had a throughput of 4 wafers per hour with a 120 W source.[15] For a 100 WPH requirement, therefore, a 3 kW source would be needed, which was not expected to be available in the foreseeable future. However, EUV photon count is determined by the number of electrons generated per photon that are collected by a photodiode. This is essentially the highly variable secondary yield of the initial photoelectron, yielding highly variable dose measurement. Data by Gullikson et al.[16] indicated ~10% natural variation of the photocurrent responsivity. More recent data for silicon photodiodes agree with this assessment.[17] Calibration of the EUV dosimeter remained a nontrivial unsolved issue.[18] The secondary electron number variability is the well-known root cause of noise in avalanche photodiodes.[19]

The highly relativistic vacuum tube free-electron lasers and synchrotron radiation sources can give better light quality than material sources, though high intensity may require development work. Existing dedicated industrial synchrotron light facilities with applications including semiconductor device fabrication. Free electron lasers offer light that is monochromatic and coherent, as well as narrow in space and angle spread. Both also offer a continuous range of available wavelengths, allowing seamless progress into the X-ray band.[20]

At SPIE 2014, TSMC reported that the 200 kW CO2 laser for their NXE:3100 EUV tool light source had a misalignment problem.[21] The laser was supposed to focus on a tin droplet that absorbs the power to generate EUV light. Missing the droplet directed the power elsewhere, leading to component damage and downtime.

Optics

EUVL is a significant departure from the deep ultraviolet lithography standard. All matter absorbs EUV radiation. Hence, EUV lithography requires a vacuum. All optical elements, including the photomask, must use defect-free Mo/Si multilayers that act to reflect light by means of interlayer interference; any one of these mirrors absorb around 30% of the incident light. This limitation can be avoided in maskless interference lithography systems. However, the latter tools are restricted to periodic patterns only.

Current EUVL systems contain at least two condenser multilayer mirrors, six projection multilayer mirrors and a multilayer object (mask). Since the optics already absorbs 96% of the EUV light, the ideal EUV source will need to be much brighter than its predecessors. EUV source development has focused on plasmas generated by laser or discharge pulses. The mirror responsible for collecting the light is directly exposed to the plasma and is therefore vulnerable to damage from high-energy ions[22][23] and other debris.[24] This damage has precluded EUV light sources from success.

Another aspect of EUVL tools is the off-axis illumination (at an angle of 6 degrees)[25] on a multilayer mask. The resulting asymmetry (leading to non-telecentricity) in the diffraction pattern causes shadowing effects that degrade pattern fidelity.[26]

EUVL's shorter wavelength also increases flare, resulting in less than perfect image quality and increased line width roughness.[27]

Heating per feature volume (e.g., 20 nm cube) is higher per EUV photon compared DUV photons, due to higher absorption in resist. In addition, EUV lithography results in more heating due to the vacuum environment, in contrast to the water cooled environment of immersion lithography.

Heating is also a particularly serious issue for multilayer mirrors. As EUV is absorbed close to the surface, the heating density is higher. As a result, water cooling is expected to be used, producing vibration that is a concern.[28]

Heating of the EUV mask pellicle (film temperature up to 750 K for 80 W incident power) is a significant concern, due to the resulting deformation and transmission decrease.[29]

A recent study found that multilayer optics contamination was highly affected by the resonant structure of the EUV mirror, influencing photoelectron generation and secondary electron yield.[30]

Since EUV is highly absorbed by all materials, even EUV optical components inside the lithography tool are susceptible to damage, mainly manifest as observable ablation.[31] Such damage is specific to EUV lithography, as conventional optical lithography systems use mainly transmissive components and do not put any component in the way of electrons, although these electrons end up depositing energy in the exposed sample substrate.

In 2012, researchers reported that a Ru-capped Mo/Si multilayer could be damaged by a single pulse (16° incidence at 13.5 nm) as low as 30 mJ/cm2, and the damage threshold can be lowered ~60% with ten pulses.[32] This was attributed to the cumulative probability of defect occurrence with multiple pulses.

Another collaboration study in 2010,[33] using Mo/Si multilayers with 42-44% reflectivity at ~28° incidence, started showing damage for single pulse at a level of ~45 mJ/cm2.

Overlay issues

Because EUV operates in a vacuum and requires reflective optics, EUV lithography tools have special overlay concerns, recently studied by IMEC, along with ASML.[34] Electrostatic chucks must be used instead of conventional vacuum chucks. Therefore the wafer clamping variability on the electrostatic chuck needs to be dealt with. A backside coating of 200 nm silicon nitride (which must be removed later to allow backside cooling[35] and heatsinking[36][37]) was found to be helpful. Other than this additional step, which also requires first protecting the device layers already patterned,[38][39] zone alignment (using all alignment marks across the wafer, not a standard subset) also provided some improvement. The vacuum environment required by EUV also leads to heating of the wafer without much dissipation. A sacrificial first wafer was found to be necessary to stabilize the chuck temperature. Moreover, the local overlay corrections due to exposure heating requires the use of a second wafer. Thus, an extra wafer per lot is required for overlay stabilization in EUV lithography. The use of reflection causes wafer exposure position to be extremely sensitive to the reticle flatness and the reticle clamp. Reticle clamp cleanliness is therefore required to be maintained.

The off-axis illumination of the reticle is also the cause of non-telecentricity in wafer defocus, which consumes most of the overlay budget of the NXE:3300 EUV scanner[40] even for design rules as loose as 100 nm pitch.[41]

Photoresist exposure

When an EUV photon is absorbed, photoelectrons and secondary electrons are generated by ionization, much like what happens when X-rays or electron beams are absorbed by matter.[42] It has been estimated that about 4 secondary electrons on average are generated for every EUV photon, although the generation volume is not definite.[43] These secondary electrons have energies of a few to tens of eV and travel tens of nanometers inside photoresist (see below) before initiating the desired chemical reaction. This is very similar to the photoelectron migration for the latent image formation in silver halide photographic films. A contributing factor for this rather large distance is the fact that polymers have significant amounts of free volume.[44] In a recent actual EUV print test,[45] it was found 30 nm spaces could not be resolved, even though the optical resolution and the photoresist composition were not the limiting factor.

In particular, for photoresists utilizing chemical amplification for higher throughput:[46][47]

e− + acid generator -> anion -> dissociated anion products

This reaction, also known as "electron attachment" or "dissociative electron attachment" is most likely to occur after the electron has essentially slowed to a halt, since it is easiest to capture at that point. The cross-section for electron attachment is inversely proportional to electron energy at high energies, but approaches a maximum limiting value at zero energy.[48] On the other hand, it is already known that the mean free path at the lowest energies (few to several eV or less, where dissociative attachment is significant) is well over 10 nm,[49][50] thus limiting the ability to consistently achieve resolution at this scale. In addition, electrons with energies < 20 eV are capable of desorbing hydrogen and fluorine anions from the resist,[51] leading to potential damage to the EUV optical system.[52]

EUV photoresist images often require resist thicknesses roughly equal to the pitch.[53] This is not only due to EUV absorption causing less light to reach the bottom of the resist but also to forward scattering from the secondary electrons (similar to low-energy electron beam lithography). Conversely, thinner resist transmits a larger fraction of incident light allowing damage to underlying films, yet requires more dosage to achieve the same level of absorption.

Since the photon absorption depth exceeds the electron escape depth, as the released electrons eventually slow down, they dissipate their energy ultimately as heat.

An EUV dose of 1 mJ/cm2 generates an equivalent photoelectron dose of 10.9 μC/cm2. Current demonstration doses exceed 10 mJ/cm2, or equivalently, 109 μC/cm2 photoelectron dose.

The use of higher doses and/or reduced resist thicknesses to produce smaller features only results in increased irradiation of the layer underneath the photoresist. This adds another significant source of photoelectrons and secondary electrons which effectively reduce the image contrast. In addition, there is increased possibility of ionizing radiation damage to the layers below.

The extent of secondary electron and photoelectrons in blurring the resolution is dependent on factors such as dose, surface contamination, temperature, etc.

It should be noted that EUV resists are also exposable by wavelengths longer than EUV, particular VUV and DUV wavelengths in the 150-250 nm range.[54]

Defects

EUVL faces specific defect issues analogous to those being encountered by immersion lithography. Whereas the immersion-specific defects are due to unoptimized contact between the water and the photoresist, EUV-related defects are attributed to the inherently ionizing energy of EUV radiation. The first issue is positive charging, due to ejection of photoelectrons[55] freed from the top resist surface by the EUV radiation. This could lead to electrostatic discharge or particle contamination as well as the device damage mentioned above. A second issue is contamination deposition on the resist from ambient or outgassed hydrocarbons, which results from EUV- or electron-driven reactions.[56] A third issue is etching of the resist by oxygen,[57] argon or other ambient gases, which have been dissociated by the EUV radiation or the electrons generated by EUV. Ambient gases in the lithography chamber may be used for purging and contamination reduction. These gases are ionized by EUV radiation, leading to plasma generation in the vicinity of exposed surfaces, resulting in damage to the multilayer optics and inadvertent exposure of the sample.[58]

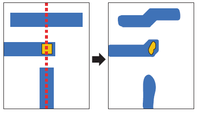

Of course mask defects are also a known source of defects for EUVL. Reducing defects on extreme ultraviolet (EUV) masks is currently one of the most critical issues to be addressed for commercialization of EUV lithography.[59] The defect core, namely the pit or particle, can originate either on the substrate, during multilayer deposition or on top of the multilayer stack. The printability of the final defect will depend on the phase change and the amplitude change of light at a given position. The net phase change and/or amplitude change adds to the intrinsic effect of the core defect and its influence on the growth of the multilayer stack during deposition. The buried defects are particularly insidious.[60]

The phase shift caused by an undetected substrate flatness variation is sufficient to produce a printable defect. The principle behind this is a quarter-wavelength deviation from the flat surface produces a half-wavelength optical path difference after reflection. The light that is reflected from the flat surface is 180 degrees out of phase with the light reflected from the quarter-wavelength deviation.[61] It has been shown that even a 1 nm deviation from flatness would lead to a substantial reduction (~20%) of the image intensity.[62] In fact, defects of atomic scale height (0.3-0.5 nm) with 100 nm FWHM can still be printable by exhibiting 10% CD impact.[63] Like a lens, any defect which effectively produces a phase shift scatters light outside the defect region. The amount of light that is scattered can be calculated. Furthermore, the edge of a phase defect will further reduce reflectivity by more than 10% if its deviation from flatness exceeds 3 degrees, due to the deviation from the target angle of incidence of 84 degrees with respect to the surface. Even if the defect height is shallow, the edge still deforms the overlying multilayer, producing an extended region where the multilayer is sloped. The more abrupt the deformation, the narrower the defect edge extension, the greater the loss in reflectivity.

Line edge roughness from mask surface roughness

The much shorter wavelength of EUV (13.5 nm) makes it more sensitive to phase fluctuations from surface roughness. Even a practical, atomic-level flatness of 0.23 nm leads to a prohibitive 2.3 nm line edge roughness (LER) for 22 nm lines and spaces, for the largest degree of coherence (expected with the use of off-axis illumination) studied.[64]

Resist issues

The introduction of EUV lithography into manufacturing confronts issues related to EUV resists. Indirectly, they have an impact on resolution capability, through tradeoffs with sensitivity and roughness.

Point spread function of resist

Kozawa et al. determined the point spread function of EUV chemically amplified resists using a basic acid generation calculation and simulation fit. The range of acid generation extended ~20 nm from the absorption point, entailing a ~40 nm resolution limit.[65]

Given that photoresists easily diffuse acid molecules, it would be no surprise that the smaller and lighter electrons produced by EUV or other ionizing radiation would diffuse faster and further, rendering the expected optical resolution meaningless.

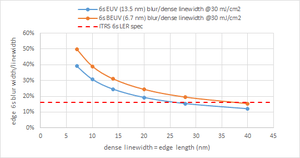

The resist blur based on print results at the end of 2008 is in the range of 10-16 nm.[66] Half-pitch resolution is still a struggle below 30 nm, and line edge roughness is still a major issue.

A study in 2011 focusing on 22 nm and 24 nm half-pitch indicated a temperature-dependent blur for the post-exposure bake process, ranging from ~5 nm at 80 °C to ~10 nm at ~110 °C. The secondary electron blur was reported to be not observed in this range.[67] The aerial images were corrected for the estimated flare (which would include any long-range secondary electron blur).

Efficient photoresist heating

Ritucci et al., reported on the improved thermal ablation efficiency for EUV wavelengths compared to DUV wavelengths.[68] Since EUV exceeds the bandgap of all materials, it is more easily absorbed than longer wavelengths, and the same dose of incident energy results in more heating; even ~100 mJ/cm2 would be hot enough to result in ablation. The resolution of chemically amplified photoresists is determined by thermally driven acid diffusion (spreading). It is worth noting that even at the ablation dose of 100 mJ/cm2, the shot noise for a 1 nm pixel is still significant (3σ/avg = 36%), which could severely impact a critical dimension (CD) for which the pixel is at least 5%, i.e., 20 nm or less.

Resist outgassing

Due to the high efficiency of absorption of EUV by photoresists, heating and outgassing become primary concerns. Organic photoresists outgas hydrocarbons[69] while metal oxide photoresists outgas water and oxygen[70] The carbon contamination is known to affect multilayer reflectivity[71] while the oxygen is particularly harmful for the ruthenium capping layers on the EUV multilayer optics.[72]

Resist polymer aggregates

Resists as polymers are well-known to have aggregates with sizes up to 80 nm.[73] Even the high-resolution resist HSQ has aggregate size reduced down to only 15–20 nm.[74] While the roughness of lines larger than the aggregate size are mildly affected by the aggregate size, below the aggregate size obviously the linewidth can be severely affected.

Resist line roughness

A model for resist line roughness caused by defects proposed in 1994 predicted that if minimum EUV dose levels for a given linewidth were not met, the resulting roughness from sidewall or base defects would be prohibitive.[75] For 20 nm linewidth and below, the minimum dose easily exceeds 100 mJ/cm2 for resists that are not chemically amplified.

Another issue is that for sub-10 nm applications, the electron beam lithography for EUV mask patterning, already burdened by throughput issues, will have practical resist difficulties for meeting the resolution requirement.[76] In fact, for 20 nm and below, the current electron-beam mask writers cannot repeatably deliver 80 nm sizes on the mask, which corresponds to 20 nm on the wafer.[77]

Projection optics scaling limits

The reduced wavelength of EUV (13.5 nm) is one factor in resolution. The other is the numerical aperture (NA) of the tool. Due to the off-axis reflective nature of the optical system, increasing NA for higher resolution is not so straightforward.

Angle of Incidence

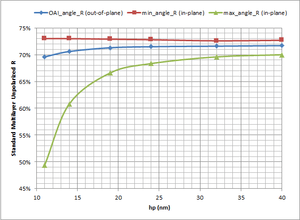

The reflective nature of the optics requires an off-axis angle of incidence onto the mask containing the pattern. For the smallest allowed pitches, the angle of incidence is extremely restricted to the Bragg's Law condition so that the smallest angle with the surface normal is given by[78] sin(minimum angle)=sin(incident angle)-0.5*wavelength/(4*pitch), with 4 being the demagnification factor (ratio of mask line pitch to target line pitch). For a wavelength of 13.5 nm and an axis-defined incident angle of 6°, a pitch of 16 nm leads to a minimum angle below 0, which is forbidden. Practically, the minimum line pitch should therefore be 19-20 nm to allow a minimum angle of 1°, 28 nm to allow the minimum angle to be reduced 2.5°. To reduce the minimum pitch, either the wavelength must be reduced or the axis-defined angle of incidence increased. When increasing the axis-defined angle of incidence, the range of all possible angles of incidence (inversely proportional to the minimum pitch, from the above equation) increases as well, requiring a larger angular bandwidth for all the multilayers making up the EUV optical components, not just the mask. This will require a significant change to the existing EUV infrastructure.

.png)

Diffraction and multilayer angle bandwidth

Resolution requirements below 20 nm require higher numerical aperture (N.A.) EUV optical systems supported by multilayer optics. However, the larger aperture necessarily entails larger angles of incidence as well as a larger range of incident angles. The multilayer currently used in EUV masks and optical systems tends to attenuate light at larger angles which is required to image tighter pitches. In particular, apodization (non-uniformity of intensity across the light entrance pupil), due to different reflectivity at different angles, becomes more severe for higher numerical apertures.[79]

For 2D patterns like dense contact holes, contrast already decreases from 80% to <75% going from 19 nm to 18 nm half-pitch, 14 nm half-pitch is already in need of multilayer tuning, and in fact, without the use of increased demagnification (above 4X) to help reduce the angles, no imaging beyond ~13 nm half-pitch is possible.[81] Such demagnification would result in large photomask substrate sizes or else multiple small fields (on different masks).

In fact, for EUV mask pitches of 8 wavelengths or less (demagnified 4x to 2 wavelengths (13-14 nm half-pitch) or less on the wafer), diffraction into the multilayer at larger angles is another source of significant image degradation, which requires intensive computation to evaluate.[82] For larger angles, the multilayer reflectance decreases significantly.[83] Rigorous EM simulations for the EUV binary mask at different magnifications have already indicated that for the standard 4X magnification, the diffraction order efficiencies starts varying significantly with new asymmetry (non-telecentricity) below 20 nm half-pitch.[84]

Telecentricity considerations alone indicate substantial difficulty using EUV below 28 nm half pitch, due to worsening telecentricity error.[85]

Etched multilayer masks[86] have been proposed to alleviate the above issues, but actually this requires the patterning of high aspect-ratio (>3.5) features on the EUV mask itself, which could lead to pattern collapse limiting the resolution to >80 nm on the mask (i.e., >20 nm on the wafer with 4x magnification).

Mask absorber thickness variation and border effect

A study published in 2011 by ASML, Brion and Zeiss found that EUV mask absorber thickness has significant effect on exposure latitude and mask error enhancement.[87] This was observed at 27-32 nm half-pitch. Furthermore, the effects were noticeably different for different conventional illumination settings. For example, for 32 nm line-and-space patterns, the optimum dose-to-size differed by more than 30%, while best bias differed by more than 4 nm, between 55.4 nm and 58 nm thickness (+/- 2.3% thickness variation). The mask absorber thickness could be optimized for size and exposure latitude for different conventional mask patterns. There remains a tradeoff of exposure latitude vs. throughput. The absorber still allows some fraction of light to pass in one direction, and the top surface itself reflects some light. The optimum absorber thickness is a linear function of the half-pitch, as well as the range of incident angles.[88] Even at the optimum absorber thickness, there is sufficient reflectivity (EUV or DUV) to present a field-to-field flare effect from the mask border. The shadowing effect is more obvious with thicker absorber.[89] The absorber thickness needs to be tightly controlled across the mask and from mask-to-mask to prevent proximity matching errors. Furthermore, the absorber thickness needs to be considered for OPC determination. With a typical CD sensitity of around 1 nm/cm2, for 27-32 nm lines, the issue is severe enough that there is a proposal to completely etch away the absorber and multilayer at the mask image field border, which entails a second layer or level of patterning in the mask fabrication, as in the case of a phase-shift mask.[90]

Source-mask optimization

Due to the effects of non-telecentricity, standard illumination pupil shapes, such as disc or annular, are not sufficient to be used for feature sizes of ~20 nm or below (10 nm node and beyond).[41] Instead certain parts of the pupil (often over 50%) must be asymmetrically excluded. The parts to be excluded depend on the pattern. There may be 200-400 illuminating points, each contributing its weight of the dose to balance the overall image through focus. Thus the shot noise effect (to be discussed later) critically affects the image position through focus, in a large population of features.

Throughput vs. resolution

The resolution of EUV lithography for future advanced faces challenges in maintaining throughput, i.e., how many wafers are processed by an EUV tool per day. These challenges arise from smaller fields, additional mirrors, and shot noise. In order to maintain throughput, the power at intermediate focus (IF) must be continually increased.

Reduced fields

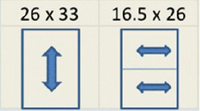

For higher numerical apertures, as noted above, it would be necessary to increase the angle of reflection in the EUV optical system. However, this could require retuning of the multilayers. As an alternative, the demagnification of the system may be increased beyond 4X, for example to 8X. This results in a reduction of the field size (standard field size is 26 mm x 33 mm). Field size reduction would also result from obscuration, i.e., putting a hole in the final mirror to allow light to pass through in order to avoid excessively wide angles [91] Higher demagnification would require either larger EUV mask substrates, or else reduced field sizes. Reduced field size entails the division of chip patterns (normally taking up 26 mm x 33 mm) among two or more conventional 6" EUV masks. A large (approaching or exceeding 500 mm2) die chip pattern such as typically used for GPUs[92] or servers[93] would have to be constructed from stitching together two or more sub-patterns from different masks.[94] Stitching of features crossing field boundaries would be critical. Also, the mask change time is a key influence on the overall throughput.[95]

Additional mirrors

As each mirror results in reflecting ~70% of the light, adding two mirrors to a 6-mirror system would result in a 50% reduction of throughput.[96]

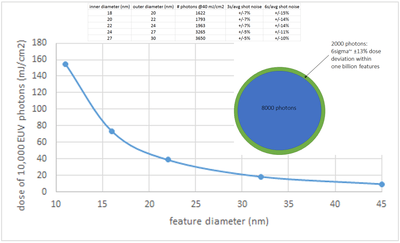

Shot noise: the statistical resolution limit

A dose sensitivity of 5 mJ/cm2 implies only several thousand EUV photons or so accumulate in such a small area. With the natural Poisson distribution due to the random arrival times of the photons, there is an expected natural dose variation of at least a few percent 3 sigma, making the exposure process fundamentally uncontrollable for features less than about 40 nm. The dose variation leads to a variation of the feature edge position, effectively becoming a blur component. Unlike the hard resolution limit imposed by diffraction, shot noise imposes a softer limit, with the main guideline being the ITRS line edge roughness (LER) spec of 8% (3s) of linewidth.[97] Increasing the dose will reduce the shot noise, but will also increase the flare dose and generate more free electrons. The free electrons will spread out before slowing to a stop. Since the free electron density is lower than the initial photon density, the shot noise is always effectively larger than expected from just considering the EUV dose.

In 2008, Intel calculated[98] that for printing one billion 30 nm contacts, ± 16% dose error @10 mJ/cm2 (scales to ± 13% dose error @15 mJ/cm2) is expected from the EUV shot noise. With acid counting, the fluctuation increases to ± 20%. This issue will affect 22 nm patterning integration. When one considers that within a 1 nm pixel, the shot noise is even more significant (>100% on 10 nm scale @10 mJ/cm2), the origin of the line edge roughness (LER) issue in EUV lithography becomes clearer.

The 2D patterns often encountered in DRAM and logic microprocessors (including multiple pattern line cutting for 11 nm node complementary lithography)[99] as well as the floating gate flash memory patterns with 2D isolation for charge trapping are more susceptible to shot noise than line-type features. It is because the 2D pattern (ideally rectangular) is defined by the number of photons in a limited area exposed above or below a certain threshold dose.

The wafer-per-hour (WPH) throughput estimates provided by EUV suppliers assume a dose of 15 mJ/cm2, which currently allows about a minute of exposure time per wafer.[100] However, the consideration of shot noise challenges this assumption, in which case EUV throughput targets can be put at risk. For example, a 40 mJ/cm2 dose in a 6-mirror EUV projection optics tool could require 900 W for 100 WPH throughput.[101]

TSMC also found that to match the shot noise performance for 193 nm light exposure at 70 nm hole size at 25-35 mJ/cm2, the required dose for EUV exposure for 30 nm hole size must be more than 4 times larger, while to scale down the CD uniformity proportionately, it would have to be more than 16 times larger.[102]

The shot noise issue is also applicable to the features patterned on masks used for EUV, targeted at 20 nm and below.[103] A 12 uC/cm2 absorbed dose used to pattern 80 nm contact holes on a mask (to print 20 nm on wafer) inevitably experiences 10% shot noise in the dose level over the population of a billion such contact holes.

The partially coherent light source is often represented as a collection of hundreds to thousands of points, each an independent source of photons.[104][105][106][107] Furthermore, the asymmetric variation of the multilayer reflectivity with respect to different angles of incidence results in source points on one side being effectively brighter than those on the other.[108] A million photons, e.g., 100 source points x 10,000 photons/point, at a dose of 10 photons/nm2, would cover a 100,000 nm2 area (~300 nm x 300 nm), far exceeding the theoretical resolution. Carl Zeiss, the maker of the EUV Aerial Image Metrology System (AIMS), recently concluded that 15,000 photons per 18 nm pixel (a dose of 68 mJ/cm2) were needed to guarantee sufficient CD fidelity.[109]

With more than 200 illuminator points in the pupil, far fewer than 100 photons are absorbed per exposed feature per pupil illuminator point. With the use of source-mask optimization as described above, even a single illuminator point is crucial for balancing the EUV image through focus for a large feature population.

Actinic mask imaging is sensitive to surface roughness but the roughness measurement of the line image is also sensitive to shot noise. It was found that the exposure dose needed to be at least 6x larger than the minimum dose used for productivity, to see noticeable reduction of roughness of 26 nm lines and spaces.[110]

The shot noise has strong bearing on the EUV source power issue mentioned above. For 10 mJ/cm2, the power at intermediate focus should be 180 W; currently it is about 20 W at high duty cycle.[111] However, significant shot noise may force minimum doses to be at least 42 mJ/cm2 for 20 nm feature size (e.g., 20 nm cuts in 20 nm half-pitch lines) and 169 mJ/cm2 for 10 nm feature size (e.g., 10 nm contacts on 14 nm half-pitch lines), therefore indicating the EUV source power to be a moving target becoming ever more difficult to reach.[112] These minimum dose values already exceed the multilayer pulse damage thresholds indicated above. Actually, the most widely acknowledged concern of such high doses is the increased resist ougassing (30 mJ/cm2 being prohibitive).[113] Furthermore, if the doses increase by at least a factor of ~3, the crosslinking of the resist polymer becomes significant.[114][115][116] As discussed below, due to high absorption, heating is more significant.

For chemically amplified resists, higher dose exposure also increases line edge roughness due to acid generator decomposition.[117]

There could be some shot noise relief for the brighfield exposures which would be used for contact hole patterns[118] with negative-tone metal oxide resists;[119] flare has more severe impact (loss of image contrast) in brightfield exposures with higher doses.[120]

Soft x-ray exposures of HSQ resist have shown 50-70 nm linewidth increase related to increased reactions beyond exposure boundaries, due to dose increase in the 100 mJ/cm2 range.[121] The increased EUV dose to reduce shot noise also increases the secondary electron distribution, which affects resolution in the same way that feature sizes are increased by increasing electron dose in electron beam lithography.

The most sensitive indicator of shot noise are features which are very sensitive to dose. A prime example is the tip-to-tip space between line ends.[122] For 10 nm design rules, a lower dose leads to extremely high sensitivity, which is a prohibitive with shot noise. However, for higher doses, almost twice the dose, the sensitivity is reduced dramatically. At the same time, the shot noise impact is reduced as well. However, there is a tradeoff that the tighter pitch is limited to a larger tip-to-tip gap. This may be addressed with more advanced line end features, generally part of the OPC technique. It may also be related to secondary electron or process-related edge blur from closer neighboring line ends. In fact, different resists with different dose sensitivities show a similar trend, with the more sensitive resist presenting a much more sensitive response of the tip-to-tip gap to dose.

ASML and Carl Zeiss SMT GmbH showed that for a 7 nm node metal design with 16 nm half-pitch, the stochastic edge placement error (SEPE) due to shot noise exceeded 3.5 nm (~22% of the feature width), though it is lower with lower pupil illumination efficiency.[123]

Impact of photoelectron and secondary electron travel on resolution

It is now recognized that for insulating materials like PMMA, low energy electrons can travel quite far (several nanometres is possible). For example, in sub-10 nm thick SiO2, negligible electron scattering is expected.[124] This is due to the fact that below the ionization potential the only energy loss mechanism is mainly through phonons and polarons.[125] It should be noted that polaronic effects are manifest more strongly in ionic crystals than polymers and covalently bonded materials.[126] In fact, polaron hopping could extend as far as 20 nm.[127]

Recent studies indicate that the EUV secondary electron range in commercial resist is practically in the range of a few nanometers.[128] This range has to be negligible (<10%) compared to the critical dimension, indicating current difficulties for sub-20 nm application.

| Material | 10 eV electron inelastic mean free path*[129][130] |

|---|---|

| Water | 10 nm |

| DNA | 5 nm |

| PMMA | 5 nm |

| SiO2 | 7 nm |

(*) On average, an electron with 10 eV energy travels this distance in the material before losing energy.

| Material | <3 eV electron attenuation length[131] |

|---|---|

| Pentacene | 7.5 ± 1.0 nm |

| Perylene | 80 ± 8.0 nm |

In a classic experiment by Feder et al. at IBM,[132] an erbium layer on a PMMA resist layer was exposed to X-rays. The erbium layer absorbed the X-rays strongly, producing low energy secondary electrons. The X-rays which were not absorbed continued to penetrate into the PMMA, where they were only lightly absorbed. Upon removal of the erbium layer and subsequent PMMA development in solvent, the resist removal rate was found to be accelerated for the top 40 nm of the PMMA film, while it was much more gradual for the rest of the film. The accelerated rate was due to the secondary electron exposure, while the gradual rate was due to the X-ray absorption. This proved the maximum secondary electron exposure range of 40 nm in this case.

K. Murata also calculated the impact of 92 eV Auger electrons emitted into a layer of PMMA from a Si substrate during X-ray exposure. The range of exposure of the PMMA was 50 nm.[133]

A more recent experiment was performed by Carter et al. at MIT and University of Wisconsin–Madison,[134] where the X-ray absorber generating the electrons was beneath the PMMA resist rather than on top of it. In this case, the accelerated dissolution of PMMA started approximately 50 nm above the substrate.

The significance of this secondary electron range is the appearance of a "proximity effect" for distances on the order of 50 nm or less.[135][136] This causes the exposure tolerance to be reduced dramatically as feature sizes decrease below this range. Even though features can still print below this range, the resolution is affected by the randomness of energy distribution. The difference in experimentally determined ranges above (40 nm vs. 50 nm) is an indication of this fundamental variability. The secondary electron exposure can also be thought of as a blur effect. The blur is generally not included in optical-only image simulations.

The proximity effect is also manifest by photoelectrons and secondary electrons leaving the top surface of the resist and then returning some tens of nanometers distance away.[137] This also can be understood in terms of the emitted electrons forming a space charge cloud above the surface which is attracted to the positively charged surface in the vertical direction but laterally disperses (in vacuum) due to the negative charge mutual repulsion.

The secondary electron proximity effect was recently demonstrated by Stanford University[138] using a scanning probe tip that emitted electrons in the 40–60 eV energy range. Dose sensitivity was demonstrated more than 25 nm away from the exposure center. It indicates that within a 50 nm range of exposure widths, the low-energy (EUV-generated) electron distribution influences the linewidth distribution. This is a new effect not seen with conventional optical lithography.

Photoelectron emission microscopy (PEEM) data was used to show that low energy electrons ~1.35 eV could travel as far as ~15 nm in SiO2, despite an average measured attenuation length of 1.18 nm.[139]

A study by the College of Nanoscale Science and Engineering (CNSE) presented at the 2013 EUVL Workshop indicated that, as a measure of EUV photoelectron and secondary electron blur, 50-100 eV electrons easily penetrated beyond 15 nm of resist thickness (PMMA or commercial resist), indicating more than 30 nm range of resist affected centered on the EUV point of absorption, for doses exceeding 200-300 uC/cm2. Furthermore, dielectric breakdown discharge is possible.[140]

A 2012 study by Synopsys and IMEC revealed that the secondary electron effect on acid generation is on the order of several nm away from the initial secondary electron generation site. In combination with shot noise and post-exposure effects, this resulted in CDs ranging from 17 to 40 nm for a 32 nm half-pitch contact hole array.[141]

Kotera et al. performed EUV photoelectron trajectory simulations, showing their range to be 30 nm.[142][143] The spread of the energy deposition by these electrons can account for the observed line edge roughness. The top layer exposure is effectively less because electrons emitted from the surface never come back.

As secondary electron generation involves inelastic scattering with momentum transfer, there will be an associated position uncertainty. As lower energy electrons have less momentum transfer, the delocalization of the secondary electron generation process tends to be higher (~nm),[144] which would have a more direct impact on LER.

Low-energy electrons exposure of 50 nm PMMA indicated that 20-30 eV electrons at doses as low as 40 uC/cm2 were sufficient to clear the resist.[145]

Shot noise vs. photoelectrons/secondary electrons

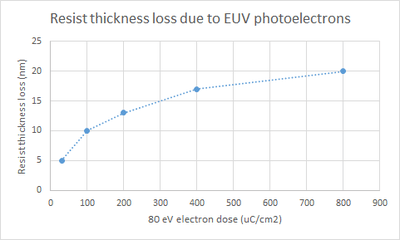

The two issues of shot noise and EUV-released electrons point out two constraining factors: 1) keeping dose high enough to reduce shot noise to tolerable levels, but also 2) avoiding too high a dose due to the increased contribution of EUV-released photoelectrons and secondary electrons to the resist exposure process, increasing the edge blur and thereby limiting the resolution. Aside from the resolution impact, higher dose also increases outgassing and limits throughput. The process of electron penetration through a resist is essentially a stochastic process; there is a finite probability that resist exposure by released electrons can occur quite far from the point of photon absorption.[146] Increasing the dose increases the number of far-reaching electrons, resulting in more extended resist loss. For an open-source resist exposed near 200 uC/cm2 by 80 eV electrons, the resist thickness lost after post-exposure bake and development was around 13 nm, while doubling the dose resulted in increasing the loss to 15 nm.[147]

Tool capacity and availability

As of early 2014, ASML targeted 70 WPH in 2014 and 125 WPH in 2015.[148] As of late 2014, wafer processing capability was 500 wafers per day with 50% availability (500 WPD0.5) or 42 WPH, with targets of 1,000 WPD0.7 or 60 WPH in 2015, and 1,500 WPD0.8 or 78 WPH in 2016. However, throughput was overconstrained with targets of 55 WPH in 2014, 75 WPH in 2015 and 125 WPH in 2016.[149]

A total of six NXE:3100 and eleven NXE:3300B systems will be installed for the purpose of learning; these models have been discontinued.[150][151][152] As of late 2014, ASML expected to ship around six NXE:3350B systems in 2015 and convert three of the eleven previously-ordered NXE:3300B systems to NXE:3350B configuration in 2015.[150][152][153] These systems will have an NA of 0.33 which requires double patterning for the 7 nm node.[154]

As of February 2015, demonstrated NXE:3300B throughput was 43 WPH.[155] Further throughput improvement depends on both source power and tool uptime.[156]

Optical proximity correction

Optical proximity correction (OPC) is expected to be implemented for EUV for 22 nm sizes and below.[122] The reason for this is the k1 parameter is already below 0.6 (corresponding to the Rayleigh resolution limit). The use of OPC entails sub-resolution features on the mask (~40 nm and smaller on the 4x mask) which need to be resolved by the electron beam mask writer. The continually increasing number of smaller and smaller OPC features per unit area continues the trend of exponentially increasing mask write times.

Patterning

Double patterning

In Intel's complementary lithography scheme at 20 nm half-pitch, EUV would be used only in a second line-cutting exposure after a first 193 nm line-printing exposure.[157] The cost may be compared to the expected multiple exposures using 193 nm light only. Some ~20 nm half-pitch patterns, e.g., 22 nm half-pitch DRAM active areas, may be patterned by a single 193 nm exposure using a special mask.[158][159] The resolution limit for EUV single patterning is ~15-19 nm half-pitch,[160] while that for ArF double patterning is 30-20 nm half-pitch, which suggests EUV double patterning rather than single patterning should succeed ArF double patterning. Taking into account the telecentricity and mask absorber complications related to asymmetry at 27 nm half-pitch,[161] the practical resolution is comparable to ArF immersion. Owing to the various current limitations on EUV reaching 10 nm half-pitch, such as the current EUV multilayer angle bandwidth for ~13-14 nm half-pitch, multiple patterning is the planned approach to extend planned 0.33 NA NXE:33X0 tools to 10 nm half-pitch.[162] At the ITRS 2012 Winter Conference, the Lithography Update indicated the use of EUV with double patterning for 14 nm half-pitch in 2017.[163]

At the Advanced Lithography 2015 SPIE conference, TSMC indicated that the 7 nm node with 30 nm pitch would require EUV to use double patterning, due to the minimum currently achievable half-pitch resolution of 16 nm.[164] EUV double patterning would therefore need to compete against triple patterning with 193 nm immersion lithography at the 7 nm node.[165] Beyond 7 nm, EUV would require a higher numerical aperture (NA) or else a shorter wavelength.

Single patterning extension

A return to extended generations of single exposure patterning would be possible with a wavelength even shorter than the 13.5 nm EUV wavelength or else higher numerical aperture (NA) tools. A much shorter wavelength (~6.7 nm) would be beyond EUV, and is often referred to as BEUV (Beyond Extreme UltraViolet).[166] Higher NA tools or different wavelengths would both pose new requirements for the multilayer optics. In particular, an NA of 0.45 using 13.5 nm wavelength already requires retuning of a few percent.[167] Increasing demagnification could avoid these issues, but the reduced field size severely affects large patterns (one die per 26 mm x 33 mm field) such as the many-core multi-billion transistor 22 nm Xeon chips.[168] A shorter wavelength would have worse shot noise effects without ensuring sufficient dose.

In 2015, ASML disclosed details of its anamorphic next-generation EUV (13.5 nm wavelength) scanner, with an NA of 0.55. Its resolution was determined to be 12 nm, not quite the 11 nm half-pitch required for the 5 nm node. By comparison, its predecessor, the NXE:3300B with 0.33 NA, only has a resolution of 19 nm, not quite the 16 nm half-pitch required for the 7 nm node.[169]

Resource requirements

| Utility | 200 W output EUV | 90 W output ArF immersion double patterning |

|---|---|---|

| Electrical power (kW) | 532 | 49 |

| Cooling water flow (L/min) | 1600 | 75 |

| Gas lines | 6 | 3 |

Source: Gigaphoton, Sematech Symposium Japan, September 15, 2010

The required utility resources are significantly larger for EUV compared to 193 nm immersion, even with two exposures using the latter. Hynix reported at the 2009 EUV Symposium that the wall plug efficiency was ~0.02% for EUV, i.e., to get 200 W at intermediate focus for 100 WPH, one would require 1MW of input power, compared to 165 kW for an ArF immersion scanner, and that even at the same throughput, the footprint of the EUV scanner was ~3x the footprint of an ArF immersion scanner, resulting in productivity loss.[170] Additionally, to confine ion debris, a superconducting magnet may be required.[171]

Demonstrations

Interference lithography at the Paul Scherrer Institute[172] has been used to demonstrate sub-10 nm line-space features.[173][174] The resist performance tested with this source does not reflect the performance expected for an EUV projection tool due to the limited contrast of projection tools.

In 1996, a collaboration between Sandia National Laboratories, University of California at Berkeley, and Lucent Technologies, produced NMOS transistors with gate lengths from 75 nm to 180 nm. The gate lengths were defined by EUV lithography.[175] The device saturation current at 130 nm gate length was ~0.2 mA/um. A 100 nm gate device showed subthreshold swing of 90 mV/decade and saturated transconductance of 250 mS/mm. A commercial NMOS at the same design rule patterned by then-state-of-the-art DUV lithography[176] showed 0.94 mA/um saturation current and 860 mS/mm saturated transconductance. The subthreshold swing in this case was less than 90 mV/decade.

In February 2008, a collaboration including IBM and AMD, based at the College of Nanoscale Science and Engineering (CNSE) in Albany, New York, used EUV lithography to pattern 90 nm trenches in the first metal layer of a 45 nm node test chip.[177] No specific details on device performance were given.[178] However, the lithographic performance details given still indicated much to be desired:[179]

- CD uniformity: 6.6%

- Overlay: 17.9 nm x, 15.6 nm y, possibly correctable to 6.7 nm x, 5.9 nm y

- Power: 1 W at wafer (>200 W required for high volume), with a dose of 3.75 mJ/cm2

- Defects: 1/sq. cm.

The high defect level may not be unexpected as AMD's 45 nm node Metal 1 design rule was 90 nm while the same EUV exposure theoretically could result in printed defects below 30 nm originating from mask defects larger than 100 nm. Optical lithography pushed beyond its natural resolution limit has a significant advantage in this regard.

Apparently, the CNSE EUV tool suffered from a well-known 16% flare problem.[180] Flare effects may be difficult to separate from the secondary electron effects discussed earlier.

Also in July 2008, IMEC printed ~60 nm contacts using their installed EUV tool.[181] Doses of 12–18 mJ/cm2 were used.

In August 2008, SEMATECH demonstrated a 22 nm half-pitch using chemically-amplified photoresist. However, even at 15 mJ/cm2, the linewidth roughness was very significant, 5–6 nm, so that even the image pitch regularity was challenged.[182]

In April 2009, IMEC fabricated 22 nm SRAM cells where the contact and Metal 1 layers (~45 nm design rule) were printed with EUV lithography.[183] However, it was acknowledged that EUV would not be ready when companies start using 22 nm. In addition, it was commented that the feature edge profiles indicated slope asymmetry related to the characteristic EUV illumination asymmetry. Whereas this demonstration only focused on a limited number of ~45 nm features, Intel's shot noise calculation above for billions of features ~30 nm indicates difficult challenges ahead for manufacturing.

In late 2009, KLA-Tencor and GlobalFoundries along with Lawrence Berkeley National Labs published a paper[184] which showed the stochastic behavior of EUV-generated secondary electrons in EUV resists. In particular, 32 nm half-pitch trenches showed significant edge roughness, width roughness and critical dimension (CD) variability.[185] It may also explain the ~ 15 nm resist blur observed in an earlier study.[186]

Device damage

MOSFETs made with Ge showed large sensitivity to EUV doses, starting to degrade even at levels of 10-20 mJ/cm2.[187]

References

- ↑ Bjorkholm, John E. (Q3'98). "EUV Lithography - The Successor to Optical Lithography?". Intel Technical Journal: 1–8. Check date values in:

|date=(help) - ↑ Mark Winter. "WebElements Periodic Table of the Elements". webelements.com.

- ↑ Tao, Y. et al. (2005). "Characterization of density profile of laser-produced Sn plasma for 13.5 nm extreme ultraviolet source". Appl. Phys. Lett. 86 (20): 201501. doi:10.1063/1.1931825.

- ↑ Coons, R. W. et al. (2010). "Comparison of EUV spectral and ion emission features from laser-produced Sn and Li plasmas". Proc. SPIE 7636: 763636. doi:10.1117/12.848318.

- ↑ Paetzel, R. et al. (2003). "Excimer lasers for superhigh NA 193-nm lithography". Proc. SPIE 5040: 1665. doi:10.1117/12.485344.

- ↑ Harilal, S. S. et al. (2006). "Spectral control of emissions from tin doped targets for extreme ultraviolet lithography". J. Phys. D 39 (3): 484. doi:10.1088/0022-3727/39/3/010.

- ↑ Trintchouk, F. et al. (2006). "XLA-300: the fourth-generation ArF MOPA light source for immersion lithography". Proc. SPIE 6154: 615423. doi:10.1117/12.658723.

- ↑ V. Bakshi, 2009 EUVL Workshop Summary, Sheraton Waikiki, Hawaii, July 13–17, 2009.

- ↑ Cymer presentation at 2007 EUV Source Workshop

- ↑ Saleh, B. E. A.; Teich, M. C. (1991). "Fundamentals of Photonics". New York: John Wiley & Sons. p. 521. ISBN 0471839655.

- ↑ T. Asayama et al., Proc. SPIE vol. 8683, 86831G (2013).

- ↑ ASML update Nov. 2013, Dublin

- ↑ "A New Light Source for EUV Lithography". ieee.org.

- ↑ Chen, F. T. (2003). "Asymmetry and thickness effects in reflective EUV masks". Proc. SPIE 5037: 347. doi:10.1117/12.483602.

- ↑ ASML update on ADT

- ↑ Gullikson, E. M. et al. (1996). "Stable silicon photodiodes for absolute intensity measurements in the VUV and soft X-ray regions" (PDF). J. Electron Spec. and Rel. Phenom. 80: 313–316. doi:10.1016/0368-2048(96)02983-0.

- ↑ Keister, J. W. (2007). "Silicon Photodiodes for Absolute Soft X-ray Radiometry" (PDF). Proc. SPIE 6689: 26. doi:10.1117/12.741601.

- ↑ Berger, K. W.; Campiotti, R. H. (2000). "Absolute dosimetry for extreme-ultraviolet lithography". Proc. SPIE 3998: 838. doi:10.1117/12.386448.

- ↑ Donati, S. (2000). Photodetectors: Devices, Circuits and Applications. Upper Saddle River, NJ: Prentice-Hall PTR. p. 182. ISBN 0130203378.

- ↑ Robert W. Hamm and Marianne E. Hamm, "The Beam Business: Accelerators in Industry", Physics Today, June 2011, pp. 49-50

- ↑ "Intel, TSMC Revive EUV Hopes". EETimes.

- ↑ H. Komori et al., Proc. SPIE 5374, pp. 839–846 (2004).

- ↑ B. A. M. Hansson et al., Proc. SPIE 4688, pp. 102–109 (2002).

- ↑ S. N. Srivastava et al., J. Appl. Phys.' 102, 023301 (2007).

- ↑ L. Peters, "Double Patterning Leads Race for 32 nm", Semiconductor International, October 18, 2007.

- ↑ M. Sugawara et al., J. Vac. Sci. Tech. B 21, 2701 (2003).

- ↑ M. Chandhok et al., J. Vac. Sci. Tech B 22, 2966 (2004).

- ↑ S. Jeong et al., Proc. SPIE 3997, 431 (2000).

- ↑ I-S. Kim et al., Proc. SPIE vol. 8322, 83222X (2012).

- ↑ N. S. Faradzhev et al., Bull. of the Russ. Acad. of Sci., Physics, vol. 74, pp. 28–32 (2010).

- ↑ F. Barkusky et al., Optics Express 18, 4346 (2010).

- ↑ M. Muller et al., Appl. Phys. A 108, 263 (2012).

- ↑ A. R. Khorsand et al., Optics Express vol. 18, 700 (2010).

- ↑ J. V. Hermans et al., Proc. SPIE 7969, 79691M (2011).

- ↑ D. Tretheway and E. S. Aydil, J. Electrochem. Soc., vol. 143, 3674 (1996).

- ↑ M. S. Bakir et al., CICC 2007, 421 (2007).

- ↑ J. A. van der Pol et al., Microelectronics Rel., 39, 863 (1999).

- ↑ "J. Mathuni et al., Wafer Backside Paper" (PDF). seconsemi.com.

- ↑ Brewer Science LED Brochure featuring Substrate Protection

- ↑ "ASML: Products - TWINSCAN NXE:3300B". asml.com.

- ↑ 41.0 41.1 X. Liu et al., Proc. SPIE vol. 9048, 90480Q (2014).

- ↑ B. L. Henke et al., J. Appl. Phys. 48, pp. 1852–1866 (1977).

- ↑ SPIE EUV08 paper by T. Kozawa and S. Tagawa

- ↑ N. Shimizu and H. Sato, 1996 IEEE Annual Report - Conference on Electrical Insulation and Dielectric Phenomena, pp. 787–790 (1996)

- ↑ Y. Ekinci et al., Microelectronic Engineering, vol. 84, pp. 700–704 (2007). Conference draft.

- ↑ T. Kozawa et al., J. Vac. Sci. Tech. B 15, pp. 2582–2586 (1997).

- ↑ T. Kozawa et al., J. Vac. Sci. Tech. B 22, pp. 3489-3492 (2004).

- ↑ E. Stoffels et al., Plasma Sources Sci. & Tech. 10, 311-317 (2001).

- ↑ M. P. Seah and W. A. Dench, Surf. Interf. Anal. 1, 2-11 (1979).

- ↑ S. Tanuma et al., Surf. Interf. Anal. 21, 165–176 (1993).

- ↑ B. Yakshinskiy et al., Intl. Symp. on EUVL 2009

- ↑ C. Song et al., Chem. Mater. 20, 3473–3479 (2008).

- ↑ H. H. Solak et al., Microel. Eng. 67–68, pp. 56–62 (2003).

- ↑ J. M. Roberts et al., Proc. SPIE 7273, 72731W (2009).

- ↑ N. Koch et al., Thin Solid Films 391, pp. 81–87 (2001).

- ↑ J. Hollenshead and L. Klebanoff, J. Vac. Sci. & Tech. B 24, pp. 118–130 (2006).

- ↑ J. Hollenshead and L. Klebanoff, J. Vac. Sci. & Tech. B 24, pp. 64–82 (2006).

- ↑ M. H. L. van der Velden et al., J. Appl. Phys. 100, 073303 (2006).

- ↑ "Getting up to speed with roadmap requirements for extreme-UV lithography". spie.org.

- ↑ "Fast Simulation Methods for Non-Planar Phase and Multilayer Defects in DUV and EUV Photomasks for Lithography". berkeley.edu.

- ↑ P. P. Naulleau et al., Optics Communications 200, pp. 27–34 (2001).

- ↑ I.-Y. Kang et al., Jap. J. Appl. Phys. vol. 44, pp. 5724–5726 (2005).

- ↑ S. Huh et al., Proc. SPIE 7271 (2009).

- ↑ B. McClinton, Ph.D. Thesis, U. C. Berkeley, 2011.

- ↑ T. Kozawa et al., Appl. Phys. Exp. 1, 027001 (2008).

- ↑ T. Watanabe and H. Kinoshita, J. Photopolymer Sci. and Tech., vol. 21, 777-784 (2008).

- ↑ R. Gronheid et al., J. Micro/Nanolith. MEMS MOEMS 10, 033004 (2011).

- ↑ A. Ritucci et al., "Damage and ablation of large band gap dielectrics induced by a 46.9 nm laser beam," March 9, 2006 report UCRL-JRNL-219656 (Lawrence Livermore National Laboratory).

- ↑ G. Denbeaux et al., 2007 European Mask and Lithography Conference.

- ↑ I. Pollentier et al., Proc. SPIE vol. 7972, 797208 (2011).

- ↑ G. Denbeaux, 2009 Intl. Workshop on EUV Lithography.

- ↑ J. Y. Park et al., J. Vac. Sci. Tech. B29, 041602 (2011).

- ↑ C. A. Cutler et al., Proc. SPIE vol. 5037, 406 (2003).

- ↑ D. Lauvernier et al., Microelectonic Eng. 75, 177–182 (2004).

- ↑ E. W. Scheckler et al., J. Vac. Sci. Tech. B 12, 2361 (1994).

- ↑ H. Yang et al., Proceedings of the 1st IEEE Intl. Conf. on Nano/Micro Engineered and Molecular Systems, pp. 391–394 (2006).

- ↑ "Litho tool explores tradeoffs at 20nm and below". electroiq.com.

- ↑ R. Petit et al., Electromagnetic Theory of Gratings, Springer-Verlag, 1980.

- ↑ K. Murakami et al., Proc. SPIE 8322, 832215 (2012).

- ↑ K. Bubke et al., Proc. SPIE vol. 6283, 628318 (2006).

- ↑ J. T. Neumann et al., May 2013 BACUS Newsletter

- ↑ M. A. Golub and A. A. Friesem, J. Opt. Soc. Am. A, 24, 687 (2007).

- ↑ Louis, E. et al. (2011). "Nanometer interface and materials control for multilayer EUV-optical applications". Prog. Surf. Sci. 86 (11–12): 255–294. doi:10.1016/j.progsurf.2011.08.001.

- ↑ C.-H. Lin et al., Microel. Eng. 84, 711 (2007).

- ↑ A. Erdmann et al., Proc. SPIE vol. 8679, 86791Q (2013).

- ↑ K. Takai et al., Proc. SPIE vol. 9235, 923515 (2014).

- ↑ N. Davydova et al., Proc. SPIE vol. 7985, 79850X (2011).

- ↑ N. Davydova et al., Proc. SPIE vol. 8166, 816624 (2011).

- ↑ E. van Setten et al., Proc. SPIE vol. 7823, 78231O (2010).

- ↑ N. Davydova et al., Proc. SPIE vol. 8880, 888027(2013).

- ↑ P. Kuerz et al., 2009 International Symposium on Extreme Ultraviolet Lithography.

- ↑ Hilbert Hagedoorn. "GeForce GTX 780 review". Guru3D.com.

- ↑ Intel Xeon E5-2600 v3

- ↑ J. T. Neumann et al., Proc. SPIE vol. 8522, 852211 (2012).

- ↑ K. Takehisa, Proc. SPIE vol. 8701, 87010T (2013).

- ↑ J. Zimmerman, Mask TWG, EUVL 2008 Symposium.

- ↑ B. Baylav, "Reduction of Line Edge Roughness (LER) in Interference-Like Large Field Lithography", PhD dissertation, p. 37, 2014.

- ↑ EUV resist TWG 2008

- ↑ "Intel Sr. Fellow Recommends Complementary Solutions for ArF Extension". nikonprecision.com.

- ↑ D. C. Brandt et al., Proc. SPIE 8322, 83221I (2012).

- ↑ ASML/Zeiss The Future of EUVL.

- ↑ Z-Y. Pan et al., Proc. SPIE vol. 6924, 69241K (2008).)

- ↑ "Globalfoundries plans production EUV by 2015". EETimes.

- ↑ L. Szu-Kai and C. C. P. Chen, Proc. SPIE vol. 7274, 727436 (2009).

- ↑ "8.1 Aerial Image Simulation of the Layout of a Multiplexer". tuwien.ac.at.

- ↑ K. Tian et al., Proc. SPIE vol. 7274, 72740C (2009).

- ↑ M. Bass (ed.), Handbook of Optics, 2.20, McGraw-Hill, 2010.

- ↑ V. Domnenko et al., Proc. SPIE 7271, 727141 (2009).

- ↑ H. Feldmann et al., Proc. SPIE 7636, 76361C (2010).

- ↑ P-Y Yan et al., Proc. SPIE 9422, 94220J (2015).

- ↑ D. C. Brandt et al., Proc. SPIE vol. 7271, 727103 (2009).

- ↑ F. T. Chen et al., Proc. SPIE 8326, 8326L (2012).

- ↑ 2013 Nissan Chemical Industries, 2013 International Workshop on EUV Lithography

- ↑ S. M. Tamboli et al., Ind. J. Chem. Tech., vol. 11, 853 (2004).

- ↑ J. N. Helbert et al., Macromolecules, vol. 11, 1104 (1978).

- ↑ J. P. Cain et al., Proc. SPIE 5751, 301 (2005).

- ↑ T. Kozawa, Jap. J. Appl. Phys. 51, 06FC01 (2012).

- ↑ R. Gronheid et al., Proc. SPIE 8322, 83220M (2012).

- ↑ J. K. Stowers et al., Proc. SPIE 7969, 796915 (2011).

- ↑ Y. Tanaka et al., Proc. SPIE 6921, 69211D (2008).

- ↑ A. G. Caster et al., J. Vac. Sci. Tech. B 28, 1304 (2010).

- ↑ 122.0 122.1 E. van Setten et al., Proc. SPIE 9231, 923108 (2014).

- ↑ S. Hsu et al., Proc. SPIE vol. 9422, 94221I (2015).

- ↑ S. Lombardo et al., J. Appl. Phys., 84, 472 (1998).

- ↑ M. Dapor et al., J. Micro/Nanolith. MEMS MOEMS 9, 023001 (2010).

- ↑ C. Kittel, Introduction to Solid State Physics, 6th ed. (John Wiley & Sons, 1986), pp. 281-3.

- ↑ P. T. Henderson et al., Proc. Natl. Acad. Sci. USA 96, 8353-8358 (1999).

- ↑ J. Torok et al., J. Photopolym. Sci. Tech. vol. 26, 625 (2013).

- ↑ D. Emfietzoglou et al., Nucl. Instr. & Meth. in Phys. Res. B 267, 45–52 (2009).

- ↑ H.-J. Fitting et al., J. Elec. Spec. & Rel. Phenom. 119, 35–47 (2001).

- ↑ S. Hino, N. Sato, H. Inokuchi, Chem. Phys. Lett. vol. 37, 494 (1976).

- ↑ R. Feder et al., J. Vac. Sci. Tech. 12, 1332 (1975).

- ↑ K. Murata, J. Appl. Phys. 57, 575 (1985).

- ↑ D. J. D. Carter et al., J. Vac. Sci. & Tech. B 15, pp. 2509–2513 (1997).

- ↑ K. Yamazaki et al., Jap. J. Appl. Phys. 36, 7552-7556 (1997).

- ↑ V. V. Ivin et al., Micr. Eng. 61-62, 343-349 (2002).

- ↑ R. Renoud et al., J. Phys. Cond. Matt. 10, 5821-5832 (1998).

- ↑ K. Wilder et al., J. Vac. Sci. Tech. B 16, 3864 (1998).

- ↑ V. W. Ballarotto et al., JVST B 20, 2514-2518 (2002).

- ↑ G. Denbeaux et al., 2013 International Workshop on EUV Lithography.

- ↑ W. Gao et al., Proc. SPIE vol. 8322, 83221D (2012).

- ↑ M. Kotera et al., Microprocesses and Nanotechnology, 2007 Digest of Papers, pp. 94–95 (2007).

- ↑ M. Kotera et al., Jap. J. Appl. Phys. vol. 47, pp. 4944–4949 (2008).

- ↑ J. Drucker and M. R. Scheinfein, Phys. Rev. B vol. 47, 15973-15975 (1993).

- ↑ A. Theta et al., Proc. SPIE vol. 9422, 94220A (2015).

- ↑ J. Torok et al., J. Photopolymer Sci. & Tech., 27, 611 (2014).

- ↑ A. Narasimhan et al., Proc. SPIE vol. 9422, 942208 (2015).

- ↑ ASML. "ASML reports 2013 results". US Securities and Exchange Commission. Retrieved 2014-07-16.

We remain on target to deliver EUV systems with a throughput of 70 wafers per hour in 2014, upgradeable to 125 wafers per hour in 2015.

- ↑ ASML. "Investor Day London". US Securities and Exchange Commission. Retrieved 2014-11-28.

- ↑ 150.0 150.1 "EX-99.2". sec.gov.

- ↑ ASML EUV tool overview

- ↑ 152.0 152.1 SPIE Europe Ltd. "ASML customers reschedule EUV tool shipments". optics.org.

- ↑ "ASML: Press - Press Releases - ASML Confirms Full-Year Sales Guidance, Supported by Solid Backlog". asml.com.

- ↑ R. Peeters et al., Proc. SPIE 9048, 90481J (2014).

- ↑ "ASML: Press - Press Releases - ASML Announces New High Mark for EUV Productivity; TSMC Images More Than 1000 Wafers in a Single Day". asml.com.

- ↑ Tiernan Ray. "ASML Gets a Lift From TSM, Though Questions on EUV Remain". Barrons.

- ↑ Intel presentation on Complementary Lithography at 2012 International Workshop on EUV Lithography

- ↑ F. T. Chen et al., Proc. SPIE vol. 8683, 868311 (2013).

- ↑ S. Owa et al., Proc. SPIE vol. 9052, 90520O (2014).

- ↑ "Semiconductor roadmapping update: Front-end technologies – Part 2". electroiq.com.

- ↑ E. van Setten et al., Proc. SPIE vol. 8352, 835205 (2012).

- ↑ ASML presentation at 2013 Semicon West

- ↑ ITRS 2012 Litho One Pager April 24, 2012

- ↑ B. J. Lin, Proc. SPIE vol. 9426, 942602 (2015).

- ↑ W. Gillijns et al., Proc. SPIE vol. 9427, 942709 (2015).

- ↑ ASML presentation at 2010 International Workshop on Extreme Ultraviolet Sources

- ↑ J. T. Neumann et al., Proc. SPIE 8522, 852211 (2012).

- ↑ Introduction to Multi-Cores

- ↑ J. van Schoot et al., Proc. SPIE vol. 9422, 94221F (2015).

- ↑ H. S. Kim, Future of Memory Devices and EUV Lithography, 2009 EUV Symposium

- ↑ H. Mizoguchi, "Laser Produced Plasma EUV Light Source Gigaphoton Update," EUVL Source Workshop, May 12, 2008.

- ↑ "Paul Scherrer Institut (PSI) ::". psi.ch.

- ↑ XIL beamline at PSI

- ↑ V. Auzelyte et al., J. Micro/Nanolith. MEMS MOEMS 8, 021204 (2009).

- ↑ K. B. Nguyen et al., J. Vac. Sci. Tech. B 14, 4188 (1996).

- ↑ S. Yang et al., IEDM '98 Technical Digest, pp. 197-200 (1998).

- ↑ B. La Fontaine et al., Proc. SPIE 6921, 69210P (2008).

- ↑ Wolfgang Gruener. "AMD reports successful production of full-field EUV test chip". TG Daily.

- ↑ "Semiconductors". pennnet.com.

- ↑ O. R. Wood II et al., Proc. SPIE 6517, 65170U (2007).

- ↑ "IMEC reports major progress in EUV". physorg.com.

- ↑ Semiconductor International: Sematech EUV Resist at 22 nm Half-Pitch

- ↑ IMEC Makes 22 nm SRAM Cells With EUV Lithography

- ↑ J. J. Biafore et al., SPIE Lithography Asia 2009, Proc. SPIE 7520, 75201P (2009).

- ↑ "KLA-Tencor brings stochastic modeling to virtual tool for EUV, DPL". electroiq.com.

- ↑ T. I. Wallow et al., Proc. SPIE 7273, 72733T (2009).

- ↑ Y-T. Chen et al., IEEE Elec. Dev. Lett., vol. 34, 1220 (2013).

Further reading

- Banqiu Wu and Ajay Kumar (May 2009). Extreme Ultraviolet Lithography. McGraw-Hill Professional, Inc. ISBN 0-07-154918-8.

- Banqiu Wu and Ajay Kumar (2009). "Extreme Ultraviolet Lithography: Towards the Next Generation of Integrated Circuits". Optics & Photonics Focus 7 (4).

Related links

| ||||||||||||