C-element

The Muller C-element, or Muller C-gate, is a commonly used asynchronous logic component originally designed by David E. Muller. It applies logical operations on the inputs and has hysteresis. The output of the C-element reflects the inputs when the states of all inputs match. The output then remains in this state until the inputs all transition to the other state. This model can be extended to the asymmetric C-element where some inputs only affect the operation in one of the transitions (positive or negative).

The Muller C-element was first used in the arithmetic logic unit (ALU) of the ILLIAC II supercomputer, proposed in 1958, and operational in 1962.

Implementations of the C-element

Different implementations have been proposed, using CMOS transistors or other existing gates.

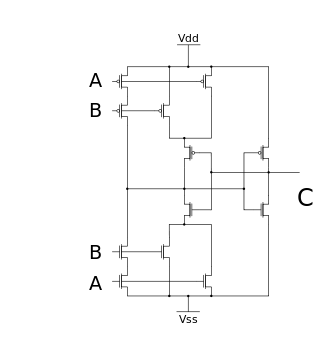

Semi-static

One of the most commonly used is the semi-static C-element, which stores its previous state with two cross-coupled inverters, similar to an SRAM cell. One of the inverters is weaker than the rest of the circuit, so it can be overpowered by the pull-up and pull-down networks.

If both inputs are 0, then the pull-up network changes the latch's state, and the C-element outputs a 0. If both inputs are 1, then the pull-down network changes the latch's state, making the C-element output a 1. Otherwise, the input of the latch is not connected to either Vdd or ground, and so the weak inverter (drawn smaller in the diagram) dominates and the latch outputs its previous state.

Static

In static CMOS, a C-element can be designed that doesn't rely on the weak feedback inverter.

Gate-level implementations

Different gate-level implementations are possible. They can be built from NAND gates or from RS latches.

Truth table

Here is the truth table for a 2-input c-gate.  denotes a "no change" condition.

denotes a "no change" condition.

| A B |  |

| 0 0 | 0 |

| 0 1 |  |

| 1 0 |  |

| 1 1 | 1 |

References

- Muller, D. E.; Bartky, W. S. (1959), "A Theory of Asynchronous Circuits", Proc. Int'l Symp. Theory of Switching, Part 1 (Harvard Univ. Press): 204–243

- "Introduction to Speed-Independent Circuits," Session IV, Proc. 2nd Ann. Symp. Switching Circuit Theory and Logical Design, AIEE, 1961, pp. 85–110. Organized by David E. Muller, this session included four papers: R.E. Miller, "An Introduction to Speed Independent Circuit Theory"; R.E. Swartwout, "One Method for Designing Speed Independent Logic for Control"; J.E. Robertson, "Problems in the Physical Realization of Speed Independent Circuits"; and D.B. Gillies, "A Flowchart Notation for the Description of a Speed Independent Control."