ARM big.LITTLE

ARM big.LITTLE is a heterogeneous computing architecture developed by ARM Holdings, coupling (relatively) slower, low-power processor cores with (relatively) more powerful and power-hungry ones. The intention is to create a multi-core processor that can adjust better to dynamic computing needs and use less power than clock scaling alone.

In October 2011, big.LITTLE was announced along with the Cortex-A7, which was designed to be architecturally compatible with the Cortex-A15.[1] In October 2012 ARM announced the Cortex-A53 and Cortex-A57 (ARMv8-A) cores, which are also compatible with each other to allow their use in a big.LITTLE chip.[2] ARM later announced the Cortex-A12 at Computex 2013 followed by the Cortex-A17 in February 2014, both can also be paired in a big.LITTLE configuration with the Cortex-A7.[3][4]

Run-state migration

There are three ways[5] for the different processor cores to be arranged in a big.LITTLE design, depending on the scheduler implemented in the kernel.[6]

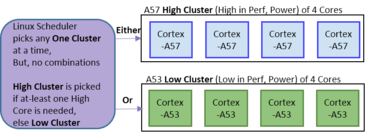

Clustered switching

The clustered model approach is the first and simplest implementation, arranging the processor into identically-sized clusters of "big" or "LITTLE" cores. The operating system scheduler can only see one cluster at a time; when the load on the whole processor changes between low and high, the system transitions to the other cluster. All relevant data is then passed through the common L2 cache, the first core cluster is powered off and the other one is activated. A Cache Coherent Interconnect (CCI) is used. This model has been implemented in the Samsung Exynos 5 Octa (5410).[7]

In-kernel switcher (CPU migration)

CPU migration via the in-kernel switcher (IKS) involves pairing up a 'big' core with a 'LITTLE' core, with possibly many identical pairs in one chip. Each pair operates as one virtual core, and only one real core is (fully) powered up and running at a time. The 'big' core is used when demand is high, the 'LITTLE' core when demand is low. When demand on the virtual core changes (between high and low), the incoming core is powered up, running state is transferred, the outgoing is shut down, and processing continues on the new core. Switching is done via the cpufreq framework. A complete big.LITTLE IKS implementation was added in Linux 3.11. big.LITTLE IKS is an improvement of Cluster Migration, the main difference is that each pair is visible to the scheduler.

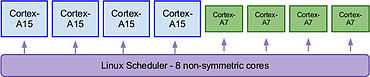

The more complex arrangement involves a non-symmetric grouping of 'big' and 'LITTLE' cores. A single chip could have one or two 'big' cores and many more 'LITTLE' cores, or vice versa. Nvidia created something similar to this with the low-power 'companion core' in their Tegra 3 SoC.

Heterogeneous multi-processing (global task scheduling)

The most powerful use model of big.LITTLE is heterogeneous multi-processing (MP), which enables the use of all physical cores at the same time. Threads with high priority or computational intensity can in this case be allocated to the "big" cores while threads with less priority or less computational intensity, such as background tasks, can be performed by the "LITTLE" cores.[8]

Upstream big.LITTLE GTS patches were incorporated into the mainline Linux kernel starting with Linux 3.10. This model has been implemented in the Samsung Exynos 5 Octa (5420, 5422, 5430, 5433), 7 Octa (7420) and Hexa (5260).[9][10]

Scheduling

The paired arrangement allows for switching to be done transparently to the operating system using the existing dynamic voltage and frequency switching (DVFS) facility. The existing DVFS support in the kernel (e.g. cpufreq in Linux) will simply see a list of frequencies/voltages and will switch between them as it sees fit, just like it does on existing hardware. However, the low-end slots will activate the 'LITTLE' core and the high-end slots will activate the 'big' core.

Alternatively, all cores may be exposed to the kernel scheduler, which will decide where each process/thread is executed. This will be required for the non-paired arrangement but could possibly also be used on paired cores. It poses unique problems for the kernel scheduler, which, at least with modern commodity hardware, has been able to assume all cores in a SMP system are equal.

Advantages of global task scheduling

- Finer-grained control of workloads that are migrated between cores. Because the scheduler is directly migrating tasks between cores, kernel overhead is reduced and power savings can be correspondingly increased.

- Implementation in the scheduler also makes switching decisions faster than in the cpufreq framework implemented in IKS.

- The ability to easily support non-symmetrical SoCs (e.g. with 2 Cortex-A15 cores and 4 Cortex-A7 cores).

- The ability to use all cores simultaneously to provide improved peak performance throughput of the SoC compared to IKS.

Implementations

| SoC | fab | big cores | LITTLE cores | GPU | Memory interface | Wireless radio technologies | Availability | Devices |

|---|---|---|---|---|---|---|---|---|

| HiSilicon K3V3 | 28 nm | 1.8 GHz dual-core Cortex-A15 | 1.2 GHz dual-core Cortex-A7 | Mali-T658 | H2 2013 | |||

| HiSilicon Kirin 920 | 28 nm | 1.7-2.0 GHz Cortex-A15 | 1.3-1.6 GHz quad-core Cortex-A7 | Mali-T628MP4 | LPDDR3 | LTE CAT6 | TBA | Huawei Honor 6 |

| Samsung Exynos 5 Octa (5410 model)[11][12] | 28 nm | 1.6-1.8 GHz quad-core Cortex-A15 | 1.2 GHz quad-core Cortex-A7 | PowerVR SGX544MP3 | 32-bit dual-channel 800 MHz LPDDR3 (12.8 GB/sec) | Q2 2013 | Exynos 5-based Samsung Galaxy S4 | |

| Samsung Exynos 5 Octa (5420 model)[13] | 28 nm | 1.8-2.0 GHz quad-core Cortex-A15 | 1.3 GHz quad-core Cortex-A7 | Mali-T628MP6 | 32-bit dual-channel 933 MHz LPDDR3e (14.9 GB/sec) | Q4 2013 | Exynos 5-based Samsung Galaxy Note 3 | |

| Samsung Exynos 5 Octa (5422 model)[10] | 28 nm | 2.1 GHz quad-core Cortex-A15 | 1.5 GHz quad-core Cortex-A7 | Mali-T628MP6 | 32-bit dual-channel 933 MHz LPDDR3e (14.9 GB/sec) | Q2 2014 | Exynos 5-based Samsung Galaxy S5, Odroid-XU3 | |

| Samsung Exynos 5 Hexa (5260 model)[10] | 28 nm | 1.7 GHz dual-core Cortex-A15 | 1.3 GHz quad-core Cortex-A7 | Mali-T624 | 32-bit dual-channel 800 MHz LPDDR3e (12.8 GB/sec) | Q2 2014 | Samsung Galaxy Note 3 Neo | |

| Samsung Exynos 5 Octa (5430 model)[14] | 20 nm | 1.8 GHz quad-core Cortex-A15 | 1.3 GHz quad-core Cortex-A7 | Mali-T628MP6 | 32-bit dual-channel 1066 MHz LPDDR3e (17.0 GB/sec) | LTE CAT6 | Q3 2014 | Samsung Galaxy Alpha[15] |

| Samsung Exynos 5 Octa (5433 model)[16] | 20 nm | 1.9 GHz quad-core Cortex-A57 | 1.3 GHz quad-core Cortex-A53 | Mali-T760MP6 | 32-bit dual-channel 825 MHz LPDDR3e (13.2 GB/sec) | LTE CAT6 | Q4 2014 | Samsung Galaxy Note 4 (SM-N910C) |

| Samsung Exynos 7 Octa (7420 model)[17] | 14 nm | 2.1 GHz quad-core Cortex-A57 | 1.5 GHz quad-core Cortex-A53 | Mali-T760MP8 | LPDDR4 | LTE | Q2 2015 | Samsung Galaxy S6 Samsung Galaxy S6 Edge |

| Renesas Mobile MP6530[18] | 28 nm | 2 GHz dual-core Cortex-A15 | 1 GHz dual-core Cortex-A7 | PowerVR SGX544 | Dual-channel LPDDR3 | LTE CAT4 | ||

| Allwinner A80 Octa[19] | 28 nm | Quad-core Cortex-A15 | Quad-core Cortex-A7 | PowerVR G6230 | Dual-channel DDR3/DDR3L/LPDDR3 or LPDDR2[20] | |||

| MediaTek MT6595[21] | 28 nm | 2.2 GHz quad-core Cortex-A17 | 1.7 GHz quad-core Cortex-A7 | PowerVR G6200 (600 MHz) | 32-bit dual-channel 933 MHz LPDDR3 (14.9 GB/sec) | LTE CAT4 | Q2 2014 | |

| MediaTek MT6595M | 28 nm | 2.0 GHz quad-core Cortex-A17 | 1.5 GHz quad-core Cortex-A7 | PowerVR G6200 (450 MHz) | 32-bit dual-channel 933 MHz LPDDR3 (14.9 GB/sec) | LTE CAT4 | Q2 2014 | |

| MediaTek MT6595 Turbo | 28 nm | 2.5 GHz quad-core Cortex-A17 | 1.7 GHz quad-core Cortex-A7 | PowerVR G6200 (600 MHz) | 32-bit dual-channel 933 MHz LPDDR3 (14.9 GB/sec) | LTE CAT4 | TBD | |

| Qualcomm Snapdragon 808 (MSM8992)[22] | 20 nm | 2.0 GHz dual-core Cortex-A57 | Quad-core ARM Cortex-A53 | Adreno 418 | 32-bit 933 MHz LPDDR3 (14.9 GB/s) | LTE Cat 6/7 | H1 2015 | |

| Qualcomm Snapdragon 810 (MSM8994)[23] | 20 nm | 2.0 GHz quad-core Cortex-A57 | Quad-core ARM Cortex-A53 | Adreno 430 | 32-bit dual-channel 1600 MHz LPDDR4 (25.6 GB/s) | LTE Cat 6/7 | H1 2015 | HTC One M9 LG G Flex 2 |

References

- ↑ "ARM Unveils its Most Energy Efficient Application Processor Ever; Redefines Traditional Power And Performance Relationship With big.LITTLE Processing" (Press release). ARM Holdings. 19 October 2011. Retrieved 2012-10-31.

- ↑ "ARM Launches Cortex-A50 Series, the World’s Most Energy-Efficient 64-bit Processors" (Press release). ARM Holdings. Retrieved 2012-10-31.

- ↑ "ARM's new Cortex-A12 is ready to power 2014's $200 midrange smartphones". The Verge. April 2014.

- ↑ "ARM Cortex A17: An Evolved Cortex A12 for the Mainstream in 2015". AnandTech. April 2014.

- ↑ Brian Jeff (18 June 2013). "Ten Things to Know About big.LITTLE". ARM Holdings. Retrieved 2013-09-17.

- ↑ George Grey (10 July 2013). "big.LITTLE Software Update". Linaro. Retrieved 2013-09-17.

- ↑ Peter Clarke (6 August 2013). "Benchmarking ARM’s big-little architecture". Retrieved 2013-09-17.

- ↑ Big.LITTLE Processing with ARM Cortex™-A15 & Cortex-A7 (PDF), ARM Holdings, September 2013, retrieved 2013-09-17

- ↑ Brian Klug (2013-09-11). "Samsung Announces big.LITTLE MP Support in Exynos 5420". AnandTech. Retrieved 2013-09-16.

- ↑ 10.0 10.1 10.2 "Samsung Unveils New Products from its System LSI Business at Mobile World Congress". Samsung Tomorrow. Retrieved 26 February 2013.

- ↑ Andrew Cunningham (10 January 2013). "Samsung’s new eight-core Exynos 5 Octa SoC promises not to hog battery". Ars Technica. Retrieved 2013-01-10.

- ↑ James Trew (9 January 2013). "Samsung announces eight-core Exynos 5 'Octa' chip at CES". Engadget. Retrieved 2013-01-10.

- ↑ "Samsung Primes Exynos 5 Octa for ARM big.LITTLE Technology with Heterogeneous Multi-Processing Capability" (Press release). Samsung Electronics. 10 September 2013. Retrieved 2013-09-17.

- ↑ "Samsung Announces Exynos 5430: First 20nm Samsung SoC". AnandTech. Retrieved 14 August 2014.

- ↑ "Samsung Introduces Galaxy Alpha, the evolution of Galaxy Design". Samsung Tomorrow. Retrieved 14 August 2014.

- ↑ "Samsung's Exynos 5433 is an A57/A53 ARM SoC". AnandTech. Retrieved 17 September 2014.

- ↑ "Samsung Announces the Galaxy S 6 and S 6 Edge". 1 March 2015. Retrieved 1 March 2015.

- ↑ MP6530 (PDF), Renesas Mobile, December 2012, retrieved 2013-09-17

- ↑ "Allwinner UltraOcta A80 processor packs a PowerVR Series6 GPU with 64 cores". Imagination. March 2014.

- ↑ "A80". Allwinner. May 2014.

- ↑ "MT6595 Octa-core LTE platform". MediaTek. April 2014.

- ↑ "Snapdragon 808 processor". Qualcomm. April 2014.

- ↑ "Snapdragon 810 processor". Qualcomm. April 2014.

Further reading

- Nicolas Pitre (15 February 2012). "Linux support for ARM big.LITTLE". LWN.net. Retrieved 2012-10-18.

- Paul McKenney (12 June 2012). "A big.LITTLE scheduler update". LWN.net. Retrieved 2012-10-18.

- Jake Edge (5 September 2012). "KS2012: ARM: A big.LITTLE update". LWN.net. Retrieved 2012-10-18.

- Jon Stokes (20 October 2011). "ARM's new Cortex A7 is tailor-made for Android superphones". Ars Technica. Retrieved 2012-10-31.

- Andrew Cunningham (30 October 2012). "ARM goes 64-bit with new Cortex-A53 and Cortex-A57 designs". Ars Technica. Retrieved 2012-10-31.

External links

- big.LITTLE Processing

- big.LITTLE Processing with ARM CortexTM-A15 & Cortex-A7 (PDF) (full technical explanation)