TILEPro64

| Produced | 2008 |

|---|---|

| Common manufacturer(s) | |

| Max. CPU clock rate | 600 MHz to 866 MHz |

| Min. feature size | 90nm |

| Cores | 64 |

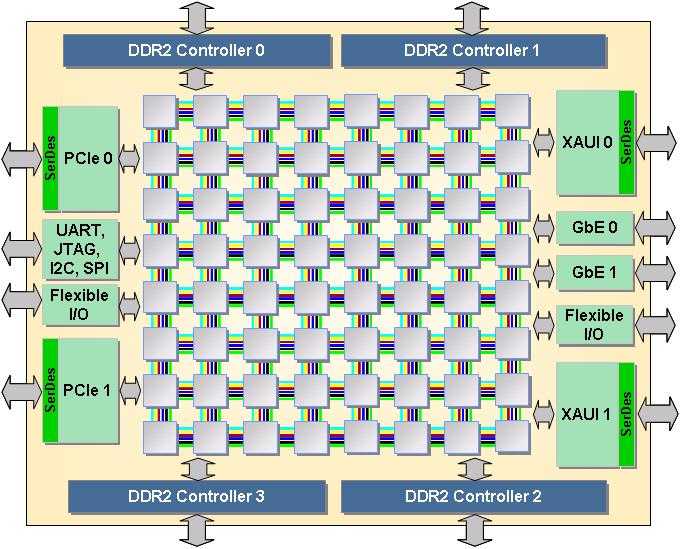

TILEPro64 is a multicore processor (Tile processor) manufactured by Tilera. It consists of a cache-coherent mesh network of 64 "tiles", where each tile houses a general purpose processor, cache, and a non-blocking router, which the tile uses to communicate with the other tiles on the processor.

The short-pipeline, in-order, three-issue cores implement a VLIW instruction set. Each core has a register file and three functional units: two integer arithmetic logic units and a load-store unit. Each of the cores ("tile") has its own L1 and L2 caches plus an overall virtual L3 cache which is an aggregate of all the L2 caches.[1] A core is able to run a full operating system on its own or multiple cores can be used to run a symmetrical multi-processing operating system.

TILEPro64 has four DDR2 controllers at up to 800MT/s, two 10-gigabit Ethernet XAUI interfaces, two four-lane PCIe interfaces, and a "flexible" input/output interface, which can be software-configured to handle a number of protocols. The processor is fabricated using a 90 nm process and runs at speeds of 600 to 866 MHz.

According to the company, Tilera targets the chip at networking equipment, digital video, and wireless infrastructure markets where the demands for computing processing are high.[2] More recently, Tilera has positioned this processor in the cloud computing space with an 8-processor (512-core) 2U server built by Quanta Computer.[3]

TILEPro is supported by the Linux kernel since version 2.6.36.

|

|

Technology

Various sources have stated the specifications of processors in the TILEPro family:

- 64 RISC processor cores

- 16 KB L1 instruction and 8 KB L1 data cache per core

- 64 KB L2 cache per core

- 4MB L3 cache is achieved through the sharing of other tiles L2 caches with hardware-managed coherency

- 90 nm manufacturing process at TSMC

- 4 integrated memory controllers supporting DDR2 SDRAM at up to 800MT/s

- supports up to 64GB of attached DDR2 memory

- Integrated high-speed I/O

- Two 4-lane PCI Express Gen1 interfaces, with root or endpoint capability

- Two 10Gbit/s Ethernet XAUI interfaces

- Two 10/100/1000 Mbit/s Ethernet RGMII interfaces

- Power consumption in the range of 19 - 23 Watts

The TILEPro family incorporates a number of enhancements over Tilera's first generation TILE64 family:

- "Distributed Dynamic Cache" (DDC) system that uses a separate mesh network to manage cache-coherency

- "TileDirect" I/O enables direct transfer of network data coherently into the processor caches

- Double the L1 instruction cache (from 8KB to 16KB), double the L2 associativity

- Memory "striping" on the DDR2 interfaces to balance the loading

- Instruction set enhancements for multimedia, unaligned data access, offset load/store instructions and memory access hints

The networking software company 6WIND provides high-performance packet processing software for the TILEPro64 platform.[4]

References

- ↑ Hodgin, Rick (September 21, 2008). "Tilera goes Pro with TILEPro64". tgdaily.com.

- ↑ Demerjian, Charlie (September 22, 2008). "Tilera releases a second 64-core chip". The Inquirer.

- ↑ Demerjian, Charlie (June 23, 2010). "Tilera gets into the cloud server business". SemiAccurate.

- ↑ http://www.6wind.com/wp-content/uploads/PDF/press/2011/6WIND-announces-availability-of-Tilera-TilePro64-support.pdf

External links

- Tilera Website

- http://www.theregister.co.uk/2008/09/23/tilera_cpu_upgrade/

- http://www.linleygroup.com/npu/Newsletter/wire080924.html#2