Retiming

Retiming is the technique of moving the structural location of latches or registers in a digital circuit to improve its performance, area, and/or power characteristics in such a way that preserves its functional behavior at its outputs. Retiming was first described by Charles E. Leiserson and James B. Saxe in 1983.[1]

The technique uses a directed graph where the vertices represent asynchronous combinational blocks and the directed edges represent a series of registers or latches (the number of registers or latches can be zero). Each vertex has a value corresponding to the delay through the combinational circuit it represents. After doing this, one can attempt to optimize the circuit by pushing registers from output to input and vice versa - much like bubble pushing. Two operations can be used - deleting a register from each input of a vertex while adding a register to all outputs, and conversely adding a register to each input of vertex and deleting a register from all outputs. In all cases, if the rules are followed, the circuit will have the same functional behavior as it did before retiming.

Formal description

The initial formulation of the retiming problem as described by Leiserson and Saxe is as follows. Given a directed graph  whose vertices represent logic gates or combinational delay elements in a circuit, assume there is a directed edge

whose vertices represent logic gates or combinational delay elements in a circuit, assume there is a directed edge  between two elements that are connected directly or through one or more registers. Let the weight of each edge

between two elements that are connected directly or through one or more registers. Let the weight of each edge  be the number of registers present along edge

be the number of registers present along edge  in the initial circuit. Let

in the initial circuit. Let  be the propagation delay through vertex

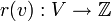

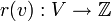

be the propagation delay through vertex  . The goal in retiming is to compute an integer lag value

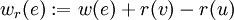

. The goal in retiming is to compute an integer lag value  for each vertex such that the retimed weight

for each vertex such that the retimed weight  of every edge is non-negative. There is a proof that this preserves the output functionality.[2]

of every edge is non-negative. There is a proof that this preserves the output functionality.[2]

Minimizing the clock period with network flow

The most common use of retiming is to minimize the clock period. A simple technique to optimize the clock period is to search for the minimum feasible period (e.g. using binary search).

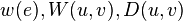

The feasibility of a clock period  can be checked in one of several ways. The linear program below is feasible if and only if

can be checked in one of several ways. The linear program below is feasible if and only if  is a feasible clock period. Let

is a feasible clock period. Let  be the minimum number of registers along any path from

be the minimum number of registers along any path from  to

to  (if such a path exists), and

(if such a path exists), and  is the maximum delay along any path from

is the maximum delay along any path from  to

to  with W(u,v) registers. The dual of this program is a minimum cost circulation problem, which can be solved efficiently as a network problem. The limitations of this approach arise from the enumeration and size of the

with W(u,v) registers. The dual of this program is a minimum cost circulation problem, which can be solved efficiently as a network problem. The limitations of this approach arise from the enumeration and size of the  and

and  matrices.

matrices.

| Given |  and a target clock period and a target clock period  | |

| Find |  | |

| Such that | ||

|

| |

|

if if  | |

Minimizing the clock period with MILP

Alternatively, feasibility of a clock period  can be expressed as a mixed-integer linear program (MILP). A solution will exist and a valid lag function

can be expressed as a mixed-integer linear program (MILP). A solution will exist and a valid lag function  will be returned if and only if the period is feasible.

will be returned if and only if the period is feasible.

| Given |  and a target clock period and a target clock period  | |

| Find |  and and  | |

| Such that | ||

|

| |

|

| |

|

| |

|

| |

Other formulations and extensions

Alternate formulations allow the minimization of the register count and the minimization of the register count under a delay constraint. The initial paper includes extensions that allow the consideration of fan-out sharing and a more general delay model. Subsequent work has addressed the inclusion of register delays,[3] load-dependent delay models,[3] and hold constraints.[4]

Problems

Retiming has found industrial use, albeit sporadic. Its primary drawback is that the state encoding of the circuit is destroyed, making debugging, testing, and verification substantially more difficult. Some retimings may also require complicated initialization logic to have the circuit start in an identical initial state. Finally, the changes in the circuit's topology have consequences in other logical and physical synthesis steps that make design closure difficult.

Alternatives

Clock skew scheduling is a related technique for optimizing sequential circuits. Whereas retiming relocates the structural position of the registers, clock skew scheduling moves their temporal position by scheduling the arrival time of the clock signals. The lower bound of the achievable minimum clock period of both techniques is the maximum mean cycle time (i.e. the total combinational delay along any path divided by the number of registers along it).

See also

- Logic Synthesis

- Electronic Design Automation

Notes

- ↑ http://citeseer.ist.psu.edu/context/96547/0

- ↑ C. E. Leiserson, J. B. Saxe, "Retiming Synchronous Circuitry," Algorithmica, Vol. 6, No. 1, pp. 5-35, 1991.

- ↑ 3.0 3.1 K. N. Lalgudi, M. C. Papaefthymiou, Retiming edge-triggered circuits under general delay models, IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol.16, no.12, pp.1393-1408, Dec. 1997.

- ↑ M. C. Papaefthymiou, Asymptotically efficient retiming under setup and hold constraints, IEEE/ACM International Conference on Computer-Aided Design, 1998.

References

- Leiserson, 1C. E.; Saxe, J. B. (1983). "Optimizing Synchronous Systems". Journal of VLSI and Computer Systems 1 (1): 41–67.

External links

A Safe and Complete Gate-Level Register Retiming Algorithm