Memory refresh

Memory refresh is the process of periodically reading information from an area of computer memory, and immediately rewriting the read information to the same area without modification, for the purpose of preserving the information.[1] Memory refresh is required in semiconductor dynamic random access memory (DRAM), the most widely used type of computer memory, and in fact is the defining characteristic of this class of memory.[2] In a DRAM chip, each bit of memory data is stored as the presence or absence of an electric charge on a small capacitor on the chip.[2][3] As time passes, the charges in the memory cells leak away, because even in a "nonconducting" state, a transistor will conduct a small amount, so without being refreshed the stored data would eventually be lost. To prevent this, external circuitry periodically reads each cell and rewrites it, restoring the charge on the capacitor to its original level. Each memory refresh cycle refreshes a succeeding area of memory cells, thus repeatedly refreshing all the cells in a consecutive cycle. This process is conducted automatically, in the background, by the memory circuitry, while the computer is on, and is transparent to the user.[2] While a refresh cycle is occurring the memory is not available for normal read and write operations, but in modern memory this "overhead" time is not large enough to significantly slow down memory operation.

Computer memory that does not require refreshing is available, called static random access memory (SRAM).[2] SRAM circuits take up more room on the semiconductor chip, because each SRAM memory cell requires 4 - 6 transistors, compared to a single transistor and a capacitor for DRAM. For this reason the storage capacity of SRAM chips is much less than DRAM, so SRAM memory is more costly per bit. Therefore DRAM is used for the main memory in computers, video games, and most other large uses of semiconductor memory. The need for extra circuitry to perform memory refresh makes DRAM circuits and their timing significantly more complicated than SRAM circuits, but the great advantages of DRAM in density and cost justify this complexity.

How DRAM refresh works

While the memory is operating, each memory cell must be refreshed repetitively, within the maximum interval between refreshes specified by the manufacturer, which is usually in the millisecond region. Refreshing does not employ the normal memory operations (read and write cycles) used to access data, but specialized cycles called refresh cycles which are generated by separate counter circuits in the memory circuitry and interspersed between normal memory accesses.[4][5]

The storage cells on a memory chip are laid out in a rectangular array of rows and columns. The read process in DRAM is destructive and removes the charge on the memory cells in an entire row, so during a normal read operation the sense amplifiers on the chip, after reading and latching the data, rewrite the data in the accessed row[2][6] before sending the bit from a single column to output. So the read electronics has the ability to refresh an entire row of memory in parallel, significantly speeding up the refresh process. A normal read or write cycle refreshes a row of memory, but normal memory accesses cannot be relied on to hit all the rows within the necessary time, necessitating a separate refresh process. Rather than use the normal read cycle in the refresh process, to save time an abbreviated cycle called a refresh cycle is used. The refresh cycle is similar to the read cycle, but executes faster for two reasons:

- For a refresh, only the row address is needed, so a column address doesn't have to be applied to the chip address circuits.

- Data read from the cells does not need to be fed into the output buffers or the data bus to send to the CPU.

The refresh circuitry must perform a refresh cycle on each of the rows on the chip within the refresh time interval, to make sure that each cell gets refreshed.

Types of refresh circuits

Many different refresh circuits have been used. Although in some early systems the microprocessor controlled refresh, with a timer triggering a periodic interrupt that ran a subroutine that performed the refresh, this meant the microprocessor could not be paused, single-stepped, or put into energy-saving hibernation without stopping the refresh process and losing the data in memory.[5] So in modern systems refresh is handled by circuits in the memory controller,[2] or increasingly on the chip itself. Some DRAM chips, such as pseudostatic RAM (PSRAM), have all the refresh circuitry on the chip, and function like static RAM as far as the rest of the computer is concerned.[7]

Usually the refresh circuitry consists of a refresh counter which contains the address of the row to be refreshed which is applied to the chip's row address lines, and a timer that increments the counter to step through the rows.[4] This counter may be part of the memory controller circuitry, or on the memory chip itself. Two scheduling strategies have been used:[5]

- Burst refresh - a series of refresh cycles are performed one after another until all the rows have been refreshed, after which normal memory accesses occur until the next refresh is required

- Distributed refresh - refresh cycles are performed at regular intervals, interspersed with memory accesses.

Burst refresh results in long periods when the memory is unavailable, so distributed refresh has been used in most modern systems,[4] particularly in real time systems. In distributed refresh, the interval between refresh cycles is

For example, the current generation of chips (DDR SDRAM) has a refresh time of 64 ms and 8,192 rows, so the refresh cycle interval is 7.8 μs.[4][8]

Recent generations of DRAM chips contain an integral refresh counter, and the memory control circuitry can either use this counter or provide a row address from an external counter. These chips have three standard ways to provide refresh, selected by different patterns of signals on the "column select" (CAS) and "row select" (RAS) lines:[5]

- "RAS only refresh" - In this mode the address of the row to refresh is provided by the address bus lines, so it is used with external counters in the memory controller.

- "CAS before RAS refresh" (CBR) - In this mode the on-chip counter keeps track of the row to be refreshed and the external circuit merely initiates the refresh cycles.[4] This mode uses less power because the memory address bus buffers don't have to be powered up. It is used in most modern computers.

- "Hidden refresh" - This is an alternate version of the CBR refresh cycle which can be combined with a preceding read or write cycle.[4] The refresh is done in parallel during the data transfer, saving time.

In the latest (2012) generation of chips the "RAS only" mode has been eliminated, and the internal counter is used to generate refresh. The chip has an additional "sleep mode", for use when the computer is in hibernation, in which an on-chip oscillator generates internal refresh cycles so that the external clock can be shut down.

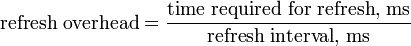

Refresh overhead

The fraction of time the memory spends on refresh, the refresh overhead, can be calculated from the system timing:[9]

For example, a recent SDRAM chip has 213 = 8 192 rows, a refresh time of 64 ms, the memory bus runs at 133 MHz, and the refresh cycle takes 4 clock cycles.[9] The time for a refresh cycle is[9]

So less than 0.4% of the memory chip's time will be taken by refresh cycles. In SDRAM chips, the memory in each chip is divided into banks which are refreshed in parallel, saving further time. So the number of refresh cycles needed is the number of rows in a single bank, given in the specifications, which in recent (2012) generations of chips has been frozen at 8 192.

Refresh interval

The maximum time interval between refreshes is standardized by JEDEC for each DRAM technology, and is specified in the manufacturer's chip specifications. It is usually in the range of milliseconds. For current (2012) DDR2 SDRAM chips it is 64 ms.[10] It depends on the ratio of charge stored in the memory cell capacitors to leakage currents. Despite the fact that the geometry of the capacitors has been shrinking with each new generation of memory chips, refresh times for DRAM have been improving; from 8 ms for 1M chips, 32 ms for 16M chips, to 64 ms for 256M chips. This improvement is achieved partly by developing transistors that leak significantly less. Longer refresh time means a smaller fraction of the device's time is occupied with refresh, leaving more time for memory accesses. Although refresh overhead occupied up to 10% of chip time in earlier DRAMs, in modern chips this fraction is less than 1%. Because the leakage currents in semiconductors increase with temperature, refresh times must be decreased at high temperature. The current generation of DDR2 SDRAM chips has a temperature-compensated refresh structure; refresh cycle time must be halved when chip case temperature exceeds 85°C (185°F).[11]

The actual persistence of readable charge values and thus data in most DRAM memory cells is much longer than the refresh time, up to 1–10 seconds.[12] However transistor leakage currents vary widely between different memory cells on the same chip. In order to make sure that all the memory cells are refreshed before a single bit is lost, manufacturers must set their refresh times conservatively short.

This frequent DRAM refresh consumes a third of the total power drawn by low-power electronics devices in standby mode. Researchers have proposed several approaches to extending battery run-time between charges by reducing the refresh rate, including temperature-compensated refresh (TCR) and retention-aware placement in DRAM (RAPID). Experiments show that in a typical off-the-shelf DRAM chip, only a few weak cells really require the worst-case 64 ms refresh interval, and even then only at the high end of its specified temperature range. At room temperature (24°C), those same weak cells need to be refreshed once every 500 ms for correct operation. If the system can avoid using the weakest 1% of pages, a typical DRAM only needs to be refreshed once a second, even at 70°C, for correct operation of the remaining 99% of the pages. Some experiments combine these two complementary techniques, giving correct operation at room temperature at refresh intervals of 10 seconds.[13]

Comparison of static and dynamic RAM

SRAM

In static random access memory (SRAM), the other type of semiconductor memory, the data is not stored as charge on a capacitor but in a pair of transistors called a flip-flop, so SRAM does not require refreshing. The two basic types of memory have advantages and disadvantages. Static memory can be considered permanent while powered on, i.e. once written the memory stays until specifically changed and thus its use tends to be simple in terms of system design. However the internal construction of each static memory cell requires six transistors, compared to the single transistor required for a dynamic RAM cell, so the density of SRAM is much lower and price-per-bit much higher than DRAM. The complexity of the static memory cell is also relatively slow to operate thus static memory tends to have lower bandwidths than equivalent dynamic storage. Writing the capacitor of the dynamic cell is very rapid and write-access times on modern dynamic storage can be in single digit nano-seconds.

DRAM

Modern DRAM modules provide the refresh circuitry on board with no requirement for motherboard circuitry, almost to the point where, at a module level, they may be thought of as static - requiring the CPU to do nothing to preserve their content

CPU based refresh

Some early microprocessors (e.g. the Zilog Z80) provided special internal registers that could provide the Row-Address Strobe (RAS) to refresh dynamic memory cells, the register being incremented on each refresh cycle. This could also be accomplished by other integrated circuits already being used in the system, if these already generated cycling accesses across RAM (e.g. the Motorola 6845). In CPUs such as the Z80, the availability of a RAS refresh was a big selling-point due to its simplifying hardware design. Here, RAS refresh is signalled by a unique combination of address and control wires during operationally redundant clock cycles (T-States), i.e. during instruction decode/execution when the buses may not be required. Instead of the bus being inactive during such T-states, the refresh register would be presented on the address bus along with a combination of control wires to indicate to the refresh circuitry.

In early versions of the Z80, the ubiquity of 16 kB RAM chips (i.e. having 128 rows) and something of a lack of foresight resulted in the R register only incrementing over a 7 bit-wide range (0–127, i.e. 128 rows); the 8th bit could be set by the user, but would be left unchanged by the internal cycling. With the rapid advent of 64 kbit+ DRAM chips (with an 8 bit RAS), extra circuitry or logic had to be built around the refresh signal to synthesize the missing 8th bit and prevent blocks of memory being lost after a few milliseconds. In some contexts, it was possible to utilise interrupts to flip the 8th bit at the appropriate time and thus cover the entire range of the R register (256 rows). Another method, perhaps more universal but also more complex in terms of hardware, was to use an 8-bit counter chip, whose output would provide the refresh RAS address instead of the R register: the refresh signal from the CPU was used as the clock for this counter, resulting in the memory row to be refreshed being incremented with each refresh cycle. Later versions and licensed "work-alikes" of the Z80 core remedied the non-inclusion of the 8th bit in automatic cycling, and modern CPUs have greatly expanded on such basic provisioning to provide rich all-in-one solutions for DRAM refresh.

Other memory technologies using refresh

Several early computer memory technologies also required periodical processes similar in purpose. These technologies include delay line memory and Williams tube. In magnetic core memory, another historical early memory technology, reading the data erased the memory cell, so each memory cell needed to be rewritten after being read.

References

- ↑ "refresh cycle" in Laplante, Phillip A. (1999). Comprehensive Dictionary of Electrical Engineering. Springer. p. 540. ISBN 3540648356.

- ↑ 2.0 2.1 2.2 2.3 2.4 2.5 Ganssle, Jack Ganssle; Tammy Noergaard, Fred Eady, Lewin Edwards, David J. Katz (2007). Embedded Hardware. Newnes. p. 106. ISBN 0750685840.

- ↑ Jacob, Bruce; Spencer Ng, David Wang (2007). Memory Systems: Cache, DRAM, Disk. Morgan Kaufmann. pp. 431–432. ISBN 0123797519.

- ↑ 4.0 4.1 4.2 4.3 4.4 4.5 Reinhardt, Steven K. (1999). "Memory, p.9-3". EECS 373 Design of Microprocessor-based Systems, Lecture Notes, Fall 1999. Electrical Engineering Dept., Univ. of Michigan. Retrieved August 26, 2012.

- ↑ 5.0 5.1 5.2 5.3 Heath, Steve (2003). Embedded Systems Design, 2nd Ed.. Newnes. pp. 88–89. ISBN 0750655461.

- ↑ Memory 1997. Integrated Circuit Engineering. 1997. p. 7.4. on The Chip Collection, Smithsonian website

- ↑ Kumar (2009). Fundamentals Of Digital Circuits, 2nd Ed.. India: PHI Learning Pvt. Ltd. p. 819. ISBN 8120336798.

- ↑ JEDEC Double Data Rate (DDR) SDRAM Specification. JESD79C. JEDEC Solid State Technology Assoc. March 2003. Retrieved August 27, 2012., p.20, on School of Engineering and Computer Science, Baylor Univ. website

- ↑ 9.0 9.1 9.2 Godse, D.A.; A.P.Godse (2008). Computer Organization. India: Technical Publications. p. 4.23. ISBN 818431356X.

- ↑ JEDEC DDR2 SDRAM Specification. JESD79-2b. JEDEC Solid State Technology Assoc. January 2005. Retrieved August 27, 2012., p.20, on School of Engineering and Computer Science, Baylor Univ. website

- ↑ JEDEC DDR2 SDRAM Specification, p.49

- ↑ Jacob, 2007, p.356

- ↑ Ravi K. Venkatesan, Stephen Herr, Eric Rotenberg. "Retention-Aware Placement in DRAM (RAPID): Software Methods for Quasi-Non-Volatile DRAM". 2006.